#### Palestine Polytechnic University

College of engineering Electrical and computer department Communication and Electronics engineering

**Graduation Project**

# GSM Security System For a car

Supervised by:

Dr. Abdallah Arman

Eng. Diaa Qasqas

Project team

Mohammad Natsheh

Wadee Awadih

Hebron – Palestine 2009/2010

GSM Security System For a car

Project team Mohammad Natsheh Wadee Awadih

Project Supervisor Dr. Abdallah Arman Eng. Diaa Qasqas

This Under-Graduate Project Report submitted to Computer and Electrical engineering "Department in College of Engineering and Technology

Palestine Polytechnic University

For accomplishment of the requirements of the bachelor degree in Communication and Electronics Engineering field

> Palestine Polytechnic University Hebron – Palestine 2009/2010

جامعة بوليتكنيك فلسطين الخليل فلسطين كلية الهندسة و التكنولوجيا دائرة الهندسة الكهربائية والحاسوب

اسم المشروع

#### GSM Security System For a car

أسماء الطلبة

محمد خليل شاكر نتشة

وديع العواوده

بناء على نظام كلية الهندسة و التكنولوجيا وإشراف ومتابعة المشرف المباشر على المشروع و موافقة أعضاء اللجنة الممتحنة تم تقديم هذا المشروع إلى دائرة الهندسة الكهربائية والحاسوب وذلك للوفاء بمتطلبات درجة البكالوريوس في الهندسة تخصص هندسة اتصالات .

توقيع المشرف C توقيع اللجنة الممتحنة

.....

توقيع رئيس الدائرة

.....

# DEDICATION

To our families for their patience

To our colleagues for their support and encouragement

To our supervisor Dr. Abdallah Arman and Eng. Diaa Qasqas for their supports

To all the people who like to know

And look for the knowledge

Mohammad Natsheh Wadee Awadih

#### Acknowledgements

We Acknowledge Palestine Polytechnic University for giving us the possibility to show some of what we have learned from it

And we acknowledge all the instructors in the Electrical and Computer Engineering department for their great impact in our education, especially the supervisors of this project Dr. Abdallah Arman and Eng. Diaa Qasqas who effected our education.

Finally we can't forget to acknowledge our great parents who scarified themselves for educating us and facilitate our life, and for all their coffee and tolerance.

Mohammad Natsheh Wadee Awadih

## Abstract

Today, the wireless Global System for Mobile Communications (GSM) in our country, has a very wide range and coverage large number of users .And this system provide many services that can be used in different applications like controlling and alarming.

The car is a very important thing in our daily life, and on the other Hand it is very expensive so we need to keep it safe and secure it from stealing.

In this project we will design and implement a GSM based security system for a car that it includes one or more sensors, which will be placed inside the car that will be able to sense a person who enter the car, and the system will give the car owner a warning by dialing his phone number then he can shut down the car and catches the intruders using other controlling signal called Dual-Tone Multi-Frequency (DTMF) signal.

## Abstract

Today, the wireless Global System for Mobile Communications (GSM) in our country, has a very wide range and coverage large number of users .And this system provide many services that can be used in different applications like controlling and alarming.

The car is a very important thing in our daily life, and on the other Hand it is very expensive so we need to keep it safe and secure it from stealing.

In this project we will design and implement a GSM based security system for a car that it includes one or more sensors, which will be placed inside the car that will be able to sense a person who enter the car, and the system will give the car owner a warning by dialing his phone number then he can shut down the car and catches the intruders using other controlling signal called Dual-Tone Multi-Frequency (DTMF) signal.

# ملخص المشروع

في الوقت الحاضر, تغطي شبكة الاتصالات الخليوية GSM العديد من المستخدمين وتشمل مناطق واسعة في بلادنا حيث تزودهم بالعديد من الخدمات التي يمكن الاستفادة منها في تطبيقات مختلفة مثل التحكم من مدى بعيد أو الاستفادة منها كجهاز انذار متقدم.

تلعب السيارة دورًا مهماً في حياتنا اليومية بالرغم من ارتفاع ثمنها. لذلك اصبح الحفاظ عليها وحمايتها من السرقات امرا مهما وملحا.

في هذا المشروع سنقوم بتصميم وتطبيق نظام حماية للسيارة بالاستفادة من الخدمات التي تزودها شبكة الاتصالات الخليويةحيث يقوم النظام بتحذير صاحب السيارة في حالة اقتحامها من قبل اللص ومحاولة سرقتها وذلك عن طريق خدمة الاتصال الصوتي بعد ذللك يتيح النظام لصاحب السيارة القدرة على تعطيلها في مكان هو موجود فيه عن طريق الاستفادة من اشارة تحكم خاصة تدعى DTMF.

#### LIST OF TABLES

# TablePageTable (1.1) Time plane for the (first semester)4Table (1.2) Time plane for the (second semester)4Table (1.3) Estimated costs and budget4Table (2.1) Call Control At commands22Table (2.2) Frequencies allocated to the push-Buttons23Table (2.3) MT8870 Output Truth27

37

Table (4.1) The relay pins

#### LIST OF FIGURES

| Figure                                         | Page |

|------------------------------------------------|------|

|                                                |      |

| Figure (2.1) GSM components                    | 8    |

| Figure (2.2) SMS flow                          | 11   |

| Figure (2.3) Structure and format of SM-MO     | 13   |

| Figure (2.4) Mobile terminated case            | 20   |

| Figure (2.5) Decoder function                  | 24   |

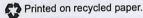

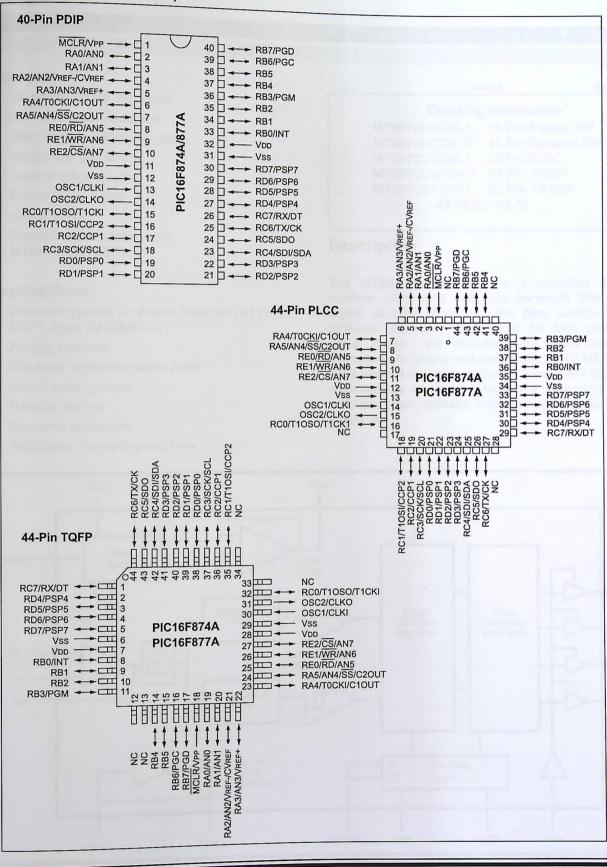

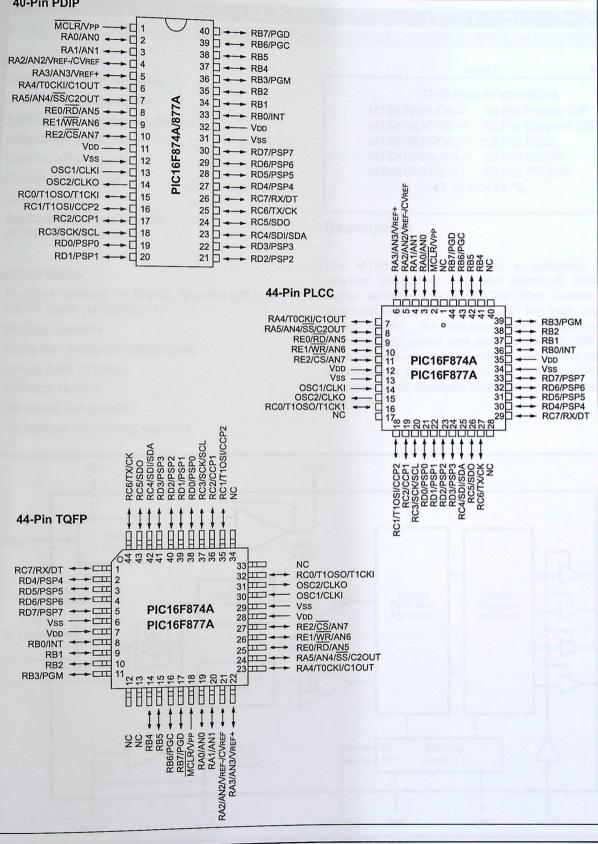

| Figure (2.6) 16f877A                           | 26   |

| Figure (2.7) (a) Input stage Inside MT8870 IC  | 27   |

| Figure (2.7) (b) Output stage Inside MT8870 IC | 28   |

| Figure (2.8) MT8870                            | 28   |

| Figure (2.9) IC 7442                           | 29   |

| Figure (3.1) Call Module                       | 32   |

| Figure (3.2) DTMF Module                       | 32   |

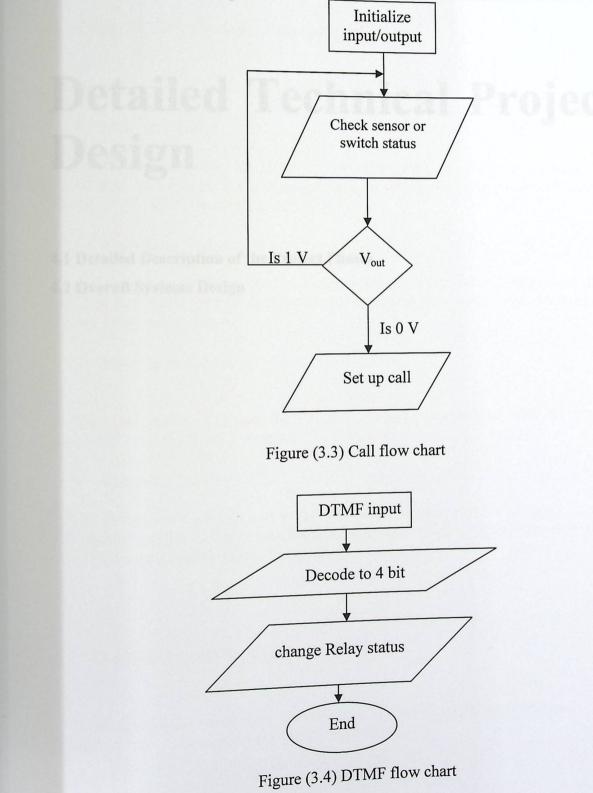

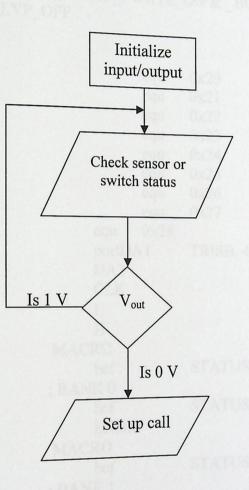

| Figure (3.3) Call flow chart                   | 33   |

| Figure (3.4) DTMF flow chart                   | 33   |

| Figure (4.1) Call transmitter                  | 36   |

| Figure (4.2) DTMF circuit                      | 37   |

| Figure (5.1) PIC communications                | 39   |

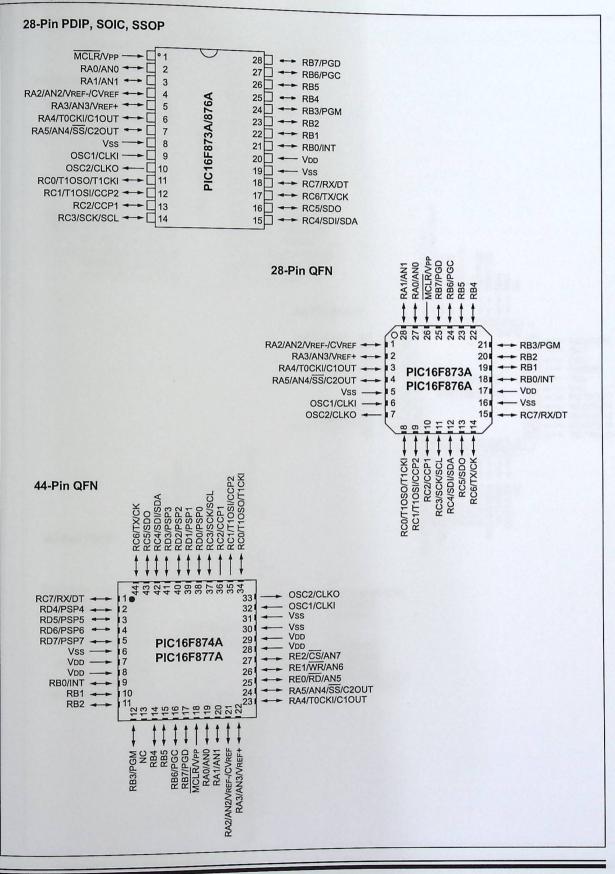

| Figure (5.2) Call flow chart                   | 40   |

| Figure (6.1) DTMF circuit                      | 49   |

| Figure (6.2) Call Transmitter                  | 50   |

| Figure (6.3) MPASMWIN Assembler                | 51   |

| Figure (6. 4) Assembly result successes        | 51   |

LE STATE

| Table of contents:                                                                                             | page   |

|----------------------------------------------------------------------------------------------------------------|--------|

| DEDICATION                                                                                                     | i      |

| Acknowledgements                                                                                               | ii     |

| Abstract                                                                                                       | iii    |

| ملخص المشروع                                                                                                   | iv     |

| LIST OF TABLES                                                                                                 | v      |

| LIST OF Figures                                                                                                | iv     |

| Table of contents                                                                                              | vii    |

|                                                                                                                |        |

| Chapter One: Introduction                                                                                      | 1      |

|                                                                                                                | 2      |

| 1.1 Overview                                                                                                   | 2<br>2 |

| 1.2 General Idea about the Project                                                                             | 2      |

| 1.3 Project Objectives                                                                                         | 2      |

| 1.4 Project Scheduling                                                                                         | 4      |

| 1.5 Estimated Cost and Budget                                                                                  | 5      |

| 1.6 Risk Management                                                                                            | 5      |

| 1.7 Report Contents                                                                                            | 7      |

| Chapter Two: Theoretical Background                                                                            |        |

| and the second termination of the second | 8      |

| 2.1 Theoretical Background related to the main idea of the Project<br>2.1.1 GSM network                        | 8      |

| 2.1.2 Short Message Service (SMS):                                                                             | 11     |

| 2.1.2 Short Message Service (SMS).<br>2.1.2.1 Implementation of point-to-point SMS in the network              | 11     |

| 2.1.2.2 SMS mobile-originated case                                                                             | 13     |

| 2.1.2.3 Classes of SMS                                                                                         | 14     |

| 2.1.2.4 Problems that can occur while sending SMS                                                              | 15     |

| 2.1.3 GSM Voice Call                                                                                           | 15     |

| 2.1.3.1 Mobile Oriented Call                                                                                   | 15     |

| 2.1.3.2 Mobile Terminated Call                                                                                 | 17     |

| 2.1.4 AT Commands                                                                                              | 21     |

| 2.1.5 Dual-Tone Multi-Frequency DTMF signal                                                                    | 22     |

| 2.2 Hardware Related to the Project                                                                            | 25     |

| 2.2.1 Microcontroller                                                                                          | 25     |

| 2.2.2 Sensors                                                                                                  | 25     |

| 2.2.3 Mobile phone                                                                                             | 25     |

| 2.3 Project Integrity                                                                                          | 26     |

| 2.4 Theoretical Background about Project Components                                                            | 26     |

| 2.4.1 PIC microcontroller                                                                                      | 26     |

| 2.4.2 3DTMF Decoder                                                                                            | 27     |

| 2.4.3 IC 7442                                                                                                  | 29     |

Law ( )

| Chapter Three: Project conceptual design                                                                                                                                                                                   | 30                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| <ul> <li>3.1 Project Objectives</li> <li>3.2 Design Realization Approach</li> <li>3.3 Project Design Block Diagram</li> <li>3.4 Project Interacting with the surrounding environment</li> <li>3.5 System Models</li> </ul> | 31<br>31<br>31<br>32<br>33 |

| Chapter Four: Detailed technical project design                                                                                                                                                                            | 34                         |

| <ul><li>4.1 Detailed Description of the project phases</li><li>4.2 Overall Systems Design</li></ul>                                                                                                                        | 35<br>35                   |

| Chapter Five: Software system design                                                                                                                                                                                       | 38                         |

| <ul> <li>5.1 Software needed for the project.</li> <li>5.2 How software system works.</li> <li>5.3 Code listing.</li> <li>5.3.1 Controller Pic</li> <li>5.3.2 Transmitter code</li> </ul>                                  | 39<br>40<br>41<br>41<br>45 |

| Chapter Six: System implementation                                                                                                                                                                                         | 48                         |

| <ul> <li>6.1 Actual project implementation</li> <li>6.2 Hardware testing</li> <li>6.2.1 DTMF Module Testing component</li> <li>6.2.2 SMS Module testing component</li> <li>6.3 Software Testing</li> </ul>                 | 48<br>49<br>49<br>50<br>51 |

| Chapter Seven: Conclusion and future works                                                                                                                                                                                 | 52                         |

| <ul><li>7.1 Conclusions</li><li>7.2 Problems</li><li>7.3 Future Work</li></ul>                                                                                                                                             | 53<br>53<br>54             |

| References                                                                                                                                                                                                                 | 55                         |

| Appendix                                                                                                                                                                                                                   | 56                         |

# **CHAPTER ONE**

# Introduction

- 1.1 Overview

- 1.2 General Idea about the Project

- 1.3 Project Objectives

- 1.4 Project Scheduling

- 1.5 Estimated Cost and Budget

- 1.6 Risk Management

- 1.7 Report Contents

#### **1.1 Overview**

Today, the wireless communication system like Global System for Mobile Communications (GSM) in our country, has a very wide range and coverage, which makes it available to build wireless security systems, one of these systems is a GSM based security system for a car.

Children and

The car is a very important thing in our daily life, and on the other Hand it is very expensive so we need to keep it safe and secure it from stealing.

In this project we will design and implement a security system that it includes one or more sensors, which will be placed inside the car that will be able to sense a person who enter the car, and the system will give you a warning then you can shut down the car and catches the intruders.

#### **1.2 General Idea about the Project**

The General idea of the project is to design a security system to prevent the thief from stealing the car. This system work when the thief breaks into the car and trigger one of the sensor so this will set up a call alarm.

When the alarm arrives to the car owner he can shut down his car engine and catch the thief using his phone.

#### **1.3 Project Objectives**

- To design a security system for a car based on GSM wireless communication system this provides a wide range for the alarm.

- To design a system that can be used to sense the surrounding area status and set up call alarm.

#### **1.4 Project Schedule**

The time planning includes two time estimation schedules, the first one show what has been done in the first semester, and the second shows the scheduling time of the second semester.

This time management clarifies each step of the project and guarantees of the overall system. The timing management divides the system hierarchy according to the following tasks:

T1: Preparing to the project : this stage of the project primarily aims at identifying the contents of it, discussing the initial information, and evaluating the project tasks and levels.

to see the California and a second statement

T2: The project analysis: the analysis process includes extensive study for all possible design options of the project.

T3: The project requirements analysis: tasks have to be implemented, equipments are needed to be provided, and data should be processed.

T4: Studying the basics of GSM network.

T5: Studying the PIC and sensors : it was necessary to study the datasheet of the PIC to ensure that it would meet the requirements of the project.

T6: Writing the documentation: the writing began from the first phase to the last one in parallel.

T7: Constructing the circuit and connections: hardware implementation of the circuits that represent the system and subsystem of our project. It was started by building prototypes.

T8: Sub-system testing : at that stage, we tested each component of the project and also each subsystem.

T9: Software implementation: it was started with installing the program of the PIC.

T10: Software testing : after completing the whole software, it was tested to check if the hardware was running appropriately.

T11: Overall system testing: we tested the project and implemented it to adjust the problems and errors and maintain it.

T12: Final documentation writing: the writing process and implementation of different stages of the project were done in parallel, in order to keep track on What had been done.

## Table (1.1) Time plane for the (first semester)

| Task | 1    | 2     | 3    | 4   | 5    | 6     | 7      | 8     | 9     | 10   | 11            | 12 | 13    | 14   | 15     | 16    |

|------|------|-------|------|-----|------|-------|--------|-------|-------|------|---------------|----|-------|------|--------|-------|

| T1   |      |       |      |     | 10 1 | 0 102 | auta   |       | 10.90 | 1180 | 18.0          |    | UV II |      | 21 142 | 1.7.4 |

| T2   |      |       |      |     |      |       |        |       |       |      |               |    |       |      |        |       |

| T3   |      |       |      |     |      |       |        |       |       |      |               |    |       |      |        |       |

| T4   | Par  | Sta   | 1.8  |     |      |       |        |       |       |      | 3             |    |       |      |        |       |

| T5   |      | faith |      |     |      | COMP  | willes | 773.5 | 1.00  |      | in the second |    | é bi  | 19 9 |        |       |

| T6   | ar p | oble  | tu . | The | levi |       |        |       |       |      |               |    |       |      |        |       |

- GULANAVAS

- Stand a Section of

Table (1.2) Time plane for the (second semester)

| Task | 17  | 18     | 19    | 20    | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 |

|------|-----|--------|-------|-------|----|----|----|----|----|----|----|----|----|----|----|----|

| T7   |     |        |       |       | 7  |    |    |    |    |    |    |    |    |    |    |    |

| T8   |     |        |       |       |    |    |    |    |    |    |    |    |    |    |    |    |

| T9   |     |        |       |       |    |    |    |    |    |    |    |    |    |    |    |    |

| T10  |     |        |       |       |    |    |    |    |    |    |    |    |    |    |    |    |

| T11  | 198 | ettici | era l | ander | 1  |    |    |    |    |    |    |    |    |    |    |    |

| T12  |     |        |       |       |    |    |    |    |    |    |    |    |    |    |    |    |

# 1.5 Estimated Costs and Budget Breakdown

This section lists the overall cost of the component that is considered in implementing the system.

The hardware components, there are many electrical chips and equipments Have to be provided are listed in table (1.3).

| Unit/task             | amount  | cost |  |  |  |

|-----------------------|---------|------|--|--|--|

| Mobile phone          | 2       | 300  |  |  |  |

| cable                 | 1       | 20   |  |  |  |

| PIC microcontroller   | 2       | 90   |  |  |  |

| MT 8870               | 1       | 20   |  |  |  |

| Printing and library  |         | 70   |  |  |  |

| Relay                 | 2       | 16   |  |  |  |

| Test board            | 2       | 30   |  |  |  |

| Transistors, crystals | 5       | 20   |  |  |  |

| Total                 | 566 NIS |      |  |  |  |

Table (1.3) Estimated costs

#### **1.6 Project Risk Management**

During the implementation of the different phases of the project, many problems and risks have to be identified and solved in the early time of the project designing and manipulation. This should be done in order to operate the project in efficiently and effectively manner.

And a least had a server

#### Hardware Risks

Device failure: the microcontroller may crash because of high voltage supply or other problems. The device operates differently from what expected.

#### **Group Risks**

- Illness of one or more of the group members

- Group meeting difficulties

#### **Project Risks:**

- Inaccurate schedule

- Insufficient budget

- Supervisor change

- Latency of devices arrival

#### **Recovery:**

- Demand device at earlier time.

- Start working on the implementation earlier.

- Use alternate devices with the same functionality and less cost.

- Try to build our own circuits that can replace unavailable devices.

#### **1.7 Report Contents**

The documentation for this project is divided into seven chapters. Each chapter concerns with a logical or physical part of the system. The followings explain briefly the contents of each chapter.

#### **Chapter 1: Introduction**

This chapter presents overview, literature review, group dependency, project scheduling and estimated cost.

#### **Chapter 2: Theoretical Background**

This chapter discusses in details the basic components used in the project and theoretical back ground.

#### Chapter 3: Project Conceptual Design

This chapter explains the design concept, introduces project objectives shows the general block diagram of the system, and explain how system works.

#### Chapter 5: Software System Design

This chapter handles the software related to our system.

#### **Chapter 6: System Implementation and Testing**

This chapter manifests the implementation procedures to be done integrate the project. Then a sequence of procedural testing will be listed the testing comprises both software and hardware testing.

#### **Chapter 7: Conclusion and Future Work**

This chapter provides the conclusions that will be concluded after working the system, and suggestion for future work.

# **CHAPTER TWO**

Children and the

# **Theoretical Background**

- 2.1 Theoretical Background related to the main idea of the project

- 2.2 Hardware Related to the Project

- 2.3 Project Integrity

- 2.4 Theoretical Background about Project Components

#### Introduction:

This chapter provides an illustrative theoretical background for our project application in general and for its each component in particularly.

#### 2.1 Theoretical background related to the project

As mentioned in the previous chapter the project is fully constructed over a communication between the mobiles installed in the car and the user mobile ,and the SMS and other information GSM network is used to establish the communication .

Now, we will introduce the all theory which related to the project.

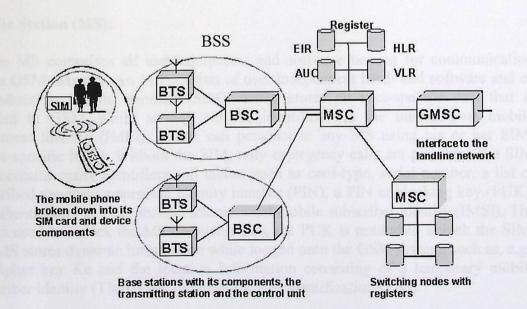

2.1.1 GSM network

#### System Architecture

GSM is very complex system architecture with many entities and interfaces Figure (2.1) gives overview of GSM system.

A GSM system consists of three subsystems, the Radio Subsystem (RSS), the Network and Switching Subsystem (NSS), and the Operation Subsystem (OSS). Each subsystem will be discussed in more detail in the following sections.

#### Radio Subsystem

The radio subsystem (RSS) comprises all radio entities the mobile stations (MS) and the base station subsystem (BSS).

Figure 2.1 shows the connection between the different GSM components.

Figure (2.1) GSM components. [1]

#### **Base Station Subsystem (BSS):**

The network comprises many BSSs, each controlled by a base station controller (BSC). The BSS performs all functions necessary to maintain radio connections to an MS, coding/decoding of voice, and rate adaptation to/from the wireless network part. Besides a BSC, the BSS contains several BTSs.

and the second second

#### **Base Transceiver Station (BTS):**

The BTS do many functions like frequency hopping channel coding and decoding and rate adaptation and encryption and decryption and paging and uplink signal measurement and it comprises all radio equipment, i.e. antennas, signal processing, amplifiers necessary for radio transmission.

A BTS can form a radio cell or, using sectorized antennas, several cells and is connected to MS via the Um interface and to the BSC via the Abis interface. The Um interface contains all the mechanisms necessary for wireless transmission (TDMA, FDMA etc.) and will be discussed in more detail in the multiplexing section The Abis interface consists of 16 or 64 kbit/s connections. A GSM cell can measure between some 100 m and 35 km depending on the environment (buildings, open space, mountains etc.) but also expected traffic.

#### **Base Station Controller (BSC):**

The BSC do many functions like management of radio channels and frequency hopping and management of terrestrial channels and encryption and decryption and paging and traffic measurement and authentication and location registry, location update the BSC basically manages the BTSs. I t reserves radio frequencies, handles the handover from one BTS to another within the BSS. The BSC also multiplexes the radio channels onto the fixed network connections at the A interface. In which these entities support other entities in the network.

#### **Mobile Station (MS):**

The MS comprises all user equipment and software needed for communication with a GSM network. An MS consists of user independent hard- and software and of the subscriber identity module (SIM), which stores all user-specific data that is relevant to GSM While an MS can be identified via the international mobile equipment identity (IMEI), a user can personalize any MS using his or her SIM, device specific IMEI. Without the SIM, only emergency calls are possible. The SIM card contains many identifiers and tables, such as card-type, serial number, a list of subscribed services, a personal identity number (PIN), a PIN unblocking key (PUK), an authentication key Ki, and the international mobile subscriber identity (IMSI). The PIN is used to unlock the MS. In such cases, the PUK is needed to unlock the SIM. The MS stores dynamic information while logged onto the GSM system, such as, e.g., the cipher key Kc and the location information consisting of a temporary mobile subscriber identity (TMSI) and the location area identification (LAI).

#### Network and Switching Subsystem

The "heart" of the GSM system is formed by the network and switching subsystem (NSS). The NSS connects the wireless network with standard public networks, performs handovers between different BSSs, comprises functions for worldwide localization of users and supports charging, accounting, and roaming of users between different providers in different countries. The NSS consists of the following switches and databases.

#### Mobile Services Switching Center (MSC):

MSCs are high-performance digital ISDN switches. They set up connections to other MSCs and to the BSCs via the A interface, and form the fixed backbone network of a GSM system. Typically, an MSC manages several BSCs in a geographical region. A gateway MSC (GMSC) has additional connections to other fixed networks, such as PSTN and ISDN. Using additional interworking functions (IWF) An MSC handles all signaling needed for connection setup, connection release and handover of connections to other MSCs.

#### Home Location Registers (HLR):

The HLR is the most important database in a GSM system as it stores all userrelevant information. This comprises static information, such as the mobile subscriber ISDN number (MSISDN), and the international mobile subscriber identity (IMSI). Dynamic information is also needed, e.g., the current location area (LA) of the MS, the mobile subscriber roaming number (MSRN), the current VLR and MSC. As soon as an MS leaves its current LA, the information in the HLR is updated. This information is necessary to localize a user in the worldwide GSM network. All these user-specific information elements only exist once for each user in a single HLR.

#### Visitor Location Registers (VLR):

The VLR associated to each MSC is a dynamic database which stores all important information needed for the MS users currently in the LA that is associated to the MSC (IMSI, MSISDN, HLR address). If a new MS comes into an LA the VLR is responsible for, it copies all relevant information for this user from the HLR. This hierarchy of VLR and HLR avoids frequent HLR updates and long-distance signaling of user information.

#### Operation Subsystem

The third part of a GSM system, the **operation subsystem** (OSS), contains the necessary functions for network operation and maintenance. The OSS possesses network entities of its own and accesses other entities via SS7 signaling.

# **Operation and Maintenance Center (OMC):**

The OMC monitors and controls all other network entities via the O interface typical OMC management functions are traffic monitoring, status reports of network entities, subscriber and security management, or accounting and billing. OMCs use the concept of telecommunication management network (TMN).

#### • Authentication Centre (AuC):

As the radio interface and mobile stations are particularly vulnerable, a separate AuC has been defined to protect user identity and data transmission. The AuC contains the algorithms for authentication as well as the keys for encryption and generates the values needed for user authentication in the HLR. The AuC may, in fact, be situated in a special protected part of the HLR.

#### • Equipment Identity Registers (EIR):

The EIR is a database for all IMEIs, i.e. it stores all device identifications registered for this network. As MSs are mobile, they can be easily stolen. With a valid SIM, anyone could use the stolen MS. The EIR has a blacklist of stolen (or locked) devices. In theory an MS is useless as soon as the owner has reported a theft. The EIR also contains a list of valid IMEIs (white list), and a list of malfunctioning devices (gray list).

#### Alarm Design options theory:

- 1. Short Message Service (SMS) alarm

- 2. Calling alarm.

#### 2.1.2 Short Message Service (SMS):

Is a communication service component of the GSM mobile communication system, using standardized communications protocols that allow the exchange of short text messages between mobile phone devices. SMS text messaging is the most widely used data application in the world.

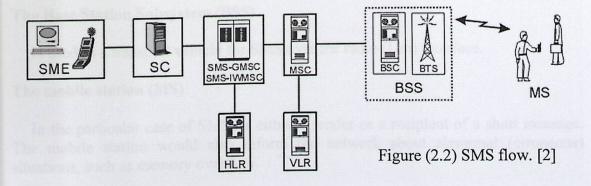

# 2.1.2.1 Implementation of point-to-point SMS in the network

Figure (2.2) show the message flow in the GSM system, the first component of the network is (SME) the short message entity which is the device that originates a short message, which is the mobile phone in our project; the point to point SMS make clear the transmission of message between two mobile station.

#### Service Center (SC):

Which receive the message from the mobile and forward it to the destination address, if it cannot reach the address, it stores the message to maximum time specified by the operator. actually the SC is integrated into the MSC and it is not part of the PLMN and the PLMN may contain Several SC according to the number of application for (SMS), and one SC may serve more than one PLMN, this would be the case if two operators in the same country share an SC.

working a start of the start and the start of the start o

#### The Short Message Service-Gate way Mobile Services Switching Center (SMS-GMSC):

Is a dedicated function within a MSC that allows it to receive a short massage from the SC, using the related (HLR) home location register in order to find out where the recipient mobile station is currently located, and then deliver the short message to the visiting MSC and, eventually, to the mobile station.

# The short message service –interworking mobile service switching center (SMS-IWMSC):

Is another dedicated function within a MSC that allows the SC to receive short messages from the MSC, this will be the case if the mobile is the originator of a short message and then the SC will transfer it to mobile station.

The (HLR) stores all the identity and user data of all the subscribers belonging to the area of the related MSC, for SMS, the relevant data in the HLR is

- The current location (MSC) of the recipient mobile station .

- Whether it is switched on and available to receive messages .

## The Mobile Services Switching Center (MSC)

Is a complete exchange system. With all of its registers, The MSC has connections to other entities of the PLMN, which allow it to gather information about the current whereabouts of a mobile station; the location is needed in order to forward messages.

#### The Visitor Location Registers (VLR):

Contains all relevant data on visiting mobile stations of the serving MSC.

## The Base Station Subsystem (BSS)

Is used as a transport vehicle for SMS over the radio (Um) interface.

#### The mobile station (MS)

In the particular case of SMS, is either a sender or a recipient of a short message. The mobile station would also inform the network about abnormal (erroneous) situations, such as memory overflow.

## 2.1.2.2 SMS mobile-originated case:

For the SMS mobile-originated case, the message flow is in a direction opposite to that in the mobile-terminated case:

1. The short message is generated in the mobile (or transferred to it from an external device). Some details need to be attended to, as explained below.

2. The short message is sent from the mobile station to the MSC.

3. The MSC passes the short message on to the SMS-IWMSC of the addressed service center.

4. The SMS-IWMSC hands the short message over to the service center. From here onward, it is the responsibility of the service center to handle the short message.

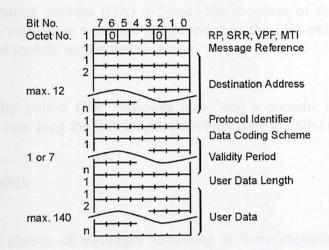

SMS-MO message frame figure (2.3) shows the structure and format of a short message-mobile originated (SM-MO) message.

figure (2.3) structure and format of SM-MO [3]

• The message type indicator (MTI) is a 2 bit value describing the kind of message contained in the frame . the message type is related to:

a) Delivering a short message from the network to the mobile station and corresponding confirmation from the mobile station.

b) Submitting a short message from the mobile station to the network and confirmation of the network.

c) Status report from the network to the mobile station about the whereabouts of the a previously sent message .

d) Issuing a command from the mobile station to the network.

- The validity period format (VPF) describes weather the validity period is present in this message, and if it is present, whether it is represented as a relative or an absolute value.

- The statues report request (SRR) indicates that the sender of this short message wants to have a confirmation that the message was delivered.

- The user data length (UDL) ,indicates the length of the following data Characters, the length is therefore, dependent on the coding scheme if the 8bit coding scheme is used, then the UDL is identical to the number of octets. If the default (7-bit coded).

• The user data (UD) contains the actual encoded message with a maximum length of 140 octets.

The message reference (MR) allows the mobile station to number the short Messages that have been sent. This MR is used when a status report is issued to the mobile station by the service center.

- The destination address (DA) indicates the recipient of this short message the address is entered as a normal phone number, the PID and DCS are, again, identical to the mobile terminated message.

- The validity period (VP) indicates how long a specific short message is valid, and how long the SC should, therefore, tries to deliver the message.

#### 2.1.2.3 Classes of SMS

There are four classes of messages according to there importance and location where they should be stored these four cases when the recipient is a mobile phone:

#### SMS Class 0:

Short messages of this class are to be displayed on the screen of the mobile station immediately, and an acknowledgment to the service center will be sent as well. This message must not necessarily be saved in the mobile station or on the SIM card.

#### SMS Class 1:

Short messages of this class should be stored by the mobile equipment in the memory of the mobile station. If this is not possible, perhaps because there is no memory available or all available memory is already full, then the message may also be stored in a different place such as on the SIM card.

#### SMS Class 2:

This message class is reserved for mobile equipment and carries SIM-specific data. The mobile station must ensure that the message is transferred to the SIM data field before sending an acknowledgment to the service center.

#### SMS Class 3:

Messages of this class are meant to be sent so that they can be forwarded to an external device such as a palmtop device or personal digital assistant.

#### 2.1.2.4 Problems that can occur while sending SMS

The permanent problems with no solution are these:

- Unknown subscriber (no such number); .

- No SMS subscription (you get only what you pay for); Illegal subscriber • (authentication for delivery failed in call setup); Illegal equipment (IMEI was blacklisted).

Here is a list of temporary problems that have solutions:

- Call barred (while barring SS and during operator-determined bar ring, the • recipient MS has no access to service).

- Absent subscriber. .

- Error in MS (e.g., no memory available). .

#### 2.1.3 GSM Voice Call

#### 2.1.3.1 Mobile Originated Call

#### **Request Access**

The MS sends a Channel Request message on the Random Access channel RACH. The BSS responds with a radio resource assignment on the Access Grant Channel

AGCH.

The MS sends a Service Request message to the BSS on the SDCCH.

#### Authentication

Before the network will provide any services to the MS, the network will require the MS to authenticate itself. The BSS sends an Authentication Request message to the MS. The RAND serves as the "challenge" for authentication.

The MS calculates the proper SRES based on the RAND that was given and sends the SRES to the BSS in an Authentication Response message.

The BSS verifies the SRES. If the SRES is correct then the MS is authenticated and allowed access to the network. The BSS will send a Service Accept message letting the MS know that the service request was received and processed.

#### **Initial Call Setup**

The MS will immediately switch to cipher mode and send a Cipher Mode Complete message.

The MS then sends a Call Setup message to the BSS. The message includes the address information (MSISDN) of the called .

The BSS assigns a TCH to the MS by sending an Assignment Command message. This message includes which Transceiver (TRX) and which Time Slot (TS) to use.

The BSS does not actually assign a TCH to the MS until the MSC sends a Call Proceeding message to the BSS indicating that the IAM has been sent.

The MS immediately switches to the assigned TCH. The MS sends an Assignment Complete message back to the BTS on the FACCH.

#### Call Setup

The MSC sends an Initial Address Message (IAM) to the GMSC. The IAM contains the MSISDN of the called party as the MS dialed it.

The MSC will also send a Call Proceeding message down to the BSS and this is when the BSS would assign a TCH to the MS, as described in step 10 above. Based on the dialed number, the GMSC decides where to route the IAM within the PSTN.

The PSTN will continue to route the IAM until it reaches the correct Switching Center and the call routing is complete. The PSTN will then establish the call circuit and send an Address Complete Message (ACM) back to the GMSC.

The GMSC then forwards the ACM back to the responsible MSC indicating that the call circuit has been established

#### Call Establishment

Once the MSC receives the ACM, it sends an ALERT message to the MS indicating that the call is going through. The BSS sends the ALERT message on the FACCH. Once the MS receives the ALERT, it will generate the ringing sound in the earpiece.

The BSS sends an alerting message the subscriber will hear the line ringing. Once the called party answers the phone, the PSTN will send an Answer message to the MSC. The MSC forwards this to the MS in a Connection message. Once the MS receives the Connection message, it switches over to voice and begins the call. All voice traffic occurs on the assigned TCH.

#### **Call Termination**

When either the caller or the called party hangs up, the call will be disconnected. Either party can initiate the disconnect. In this example, the MS initiates the disconnect. The MS sends a Disconnect message to the BTS on the FACCH.

The BSS forwards the DISC to the MSC. Once the MSC receives the DISC message, it sends a Release (REL) message through the GMSC to the PSTN as well as down through the BSS to the MS.

The MS responds by sending a Release Complete message to the BSS on the FACCH. The BSS forwards the Release Complete message up to the MSC. Once the MSC receives the Release Complete message the call is considered ended from the call control perspective. Although the call has ended, the BSS still has a TCH allocated to the MS. The MSC sends a Channel Release message to the BSS. The BSS forwards the Channel Release message to the MS.

The MS responds with a disconnect (LAPDm) message and returns to an idle mode. The BSS reallocates the channel for other call or releases the TRX.

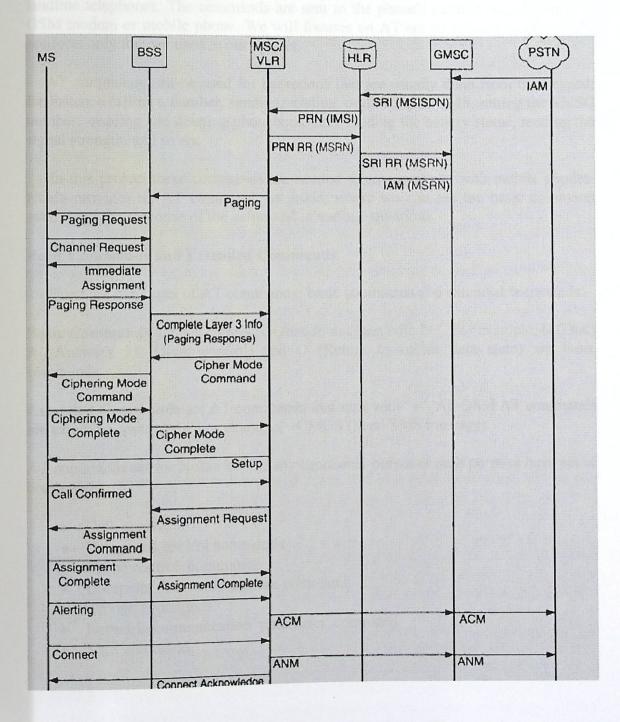

#### 2.1.3.2 Mobile Terminated Call

# Route Establishment to find the MSC/VLR

The calling party dials the MSISDN for the mobile subscriber. The PSTN identifies the network (PLMN) that the dialed MSISDN belongs to and will locate a GMSC for that network. The PSTN sends an Initial Address message to the GMSC.

The GMSC forwards the MSISDN to the HLR and requests routing information for it. The HLR looks up the MSISDN and determines the IMSI and the SS7 address for the MSC/VLR that is servicing the MS. The HLR then contacts the servicing MSC/VLR and asks it to assign a Mobile Station Routing Number (MSRN) to the call.

The MSC/VLR allocates the MSRN and forwards it to the HLR.

The HLR forwards the MSRN as well as routing information for the servicing MSC/VLR to the GMSC.

The GMSC sends an Initial Addressing message to the servicing MSC/VLR and uses the MSRN to route the call to the MSC/VLR. Once the servicing MSC/VLR receives the call, the MSRN can be released and may be made available for reassignment.

#### **Paging the Mobile Station**

The MSC/VLR then orders all of its BSCs and BTSs to page the MS. Since the MSC/VLR does not know exactly which BSC and BTS the MS is monitoring, the page will be sent out across the entire Location Area.

#### **Initial Setup**

The MS receives the Page Request on the PCH. The MS recognizes that the page is intended for it, based on a TMSI or an IMSI.

The MS sends a Channel Request message on the RACH.

The BSS responds on the AGCH by sending an Immediate Assignment message which assigns an SDCCH to the MS. At this point, the network does not know that the MS is the one that it is paging; it only knows that this MS wants access to the network.

The MS immediately switches to the assigned SDCCH and sends a Paging Response message on the SDCCH. This lets the network know that the MS is responding to its page.

#### Authentication

Before the network will provide any services to the MS, the network will require the MS to authenticate itself. The BSS sends an Authentication Request message to the MS. The RAND serves as the "challenge" for authentication.

The MS calculates the proper SRES based on the RAND that was given and sends the SRES to the BSS in an Authentication Response message.

The BSS verifies the SRES. If the SRES is correct then the MS is authenticated and allowed access to the network.

Once the MSC/VLR has authenticated the MS, it will order the BSS and MS to switch to cipher mode using the cipher mode command message. Once the MS in encryption mode, the VLR will normally assign a new TMSI to the MS.

#### Establishing a Channel

Once the MS is authenticated and in encryption mode, The MSC sends a Setup Message to the BSS, the BSS forwards the SETUP message to the MS on the assigned SDCCH. The setup message may include the Calling Line Identification Presentation, which is essentially caller ID.

The MS responds by sending a Call Confirmed message; which indicates that the MS is able to establish the requested connection. The BSS relays the message up to the MSC.

#### Call Setup

The BSS then sends an Assignment Command message to the MS on the assigned SDCCH. The Assignment Command message assigns a Traffic Channel (TCH) to the MS.

The MS immediately switches to the TCH and responds with an Assignment Complete message on the FACCH. The MS begins ringing once it has established the TCH.

The MS sends an ALERT message to the MSC on the FACCH. The BSS forwards the ALERT message through the PSTN to the calling party and the caller hears the line ringing.

#### **Call Establishment**

Once the user answers the call (by pressing the send button), the MS will send a *Connect* CON message to the MSC. The Connect message is forwarded back to the caller's switch to activate the call.

The MSC sends a Connect Acknowledge message to the MS and the call is established.

#### **Call Disconnect**

Disconnect happens the same way as for any other call. In this example, the calling party initiates the disconnect.

When the calling party hangs up, the calling party's switch initiates a Release message. The message is forwarded to the serving MSC, which is then forwarded to the BSS.

The BSS will send a Disconnect message to the MS on the FACCH.

The MS confirms release of the call by sending a Release message on the FACCH, which is forwarded to the MSC.

The MSC sends e Release Complete message through the BSS to the MS. As far as call control (CC) is concerned, the connection has been terminated.

The MS still has a TCH assigned to it, so the BSS sends a Channel Release message to the MS. This releases the radio resource on the Air Interface.

The MS responds be sending a final Disconnect message and returns to idle.

Figure (2.4) Mobile terminated case [3]

#### 2.1.4 AT commands:

#### **Definition:**

AT commands are also known as Hayes AT commands. There are different views to understand the meanings of "AT". Some call it "Attention Telephone", whereas others interpret it as "Attention Terminal" commands.

AT commands allow giving instructions to both mobile devices and ordinary landline telephones. The commands are sent to the phone's modem, which can be a GSM modem or mobile phone. We will focuses on AT commands on Nokia's GSM products only that we used in our project.

AT commands can be used for operations that are usually done from the keypad, for instance calling a number, sending, reading, or deleting an SMS, setting the SMSC number, reading and deleting phonebook data, reading the battery status, reading the signal strength, and so on.

In this project these commands are needed to communicate with mobile phones. Nokia provides an AT command set guide, where we can see the basic command syntax and the response of the command in various situations.

#### **Basic Commands and Extended Commands**

There are two types of AT commands: basic commands and extended commands.

**Basic Commands** are AT commands that do not start with "+". For example, D (Dial) A (Answer), H (Hook control) and O (Return to online data state) are basic commands

**Extended Commands** are AT commands that start with "+". All GSM AT commands are extended commands. For example, +CMGS (Send SMS message).

AT commands set for Nokia have many functional purposes each purpose have set of commands:

- Call control

- Data cared control commands

- Phone control commands

- Computer data card interface command

- Service commands

- Network communication parameter command

- SMS command

| command | description                  |  |  |  |  |

|---------|------------------------------|--|--|--|--|

| ATA     | Answer command               |  |  |  |  |

| ATD     | Dial command                 |  |  |  |  |

| ATH     | Hang up call                 |  |  |  |  |

| AT+CSTA | Select type of address       |  |  |  |  |

| AT+CRC  | Cellular result codes        |  |  |  |  |

| ATO     | Go on-line                   |  |  |  |  |

| ATP     | Set pulse dial as default    |  |  |  |  |

| AT+CSAS | Save settings                |  |  |  |  |

| AT+CRES | Restore setting              |  |  |  |  |

| AT+CNMI | New message indication to TE |  |  |  |  |

In our project we interesting in the AT commands which listed in table (2.1)

Table (2.1) Call Control At commands

#### 2.1.5 Dual-Tone Multi-Frequency DTMF signal

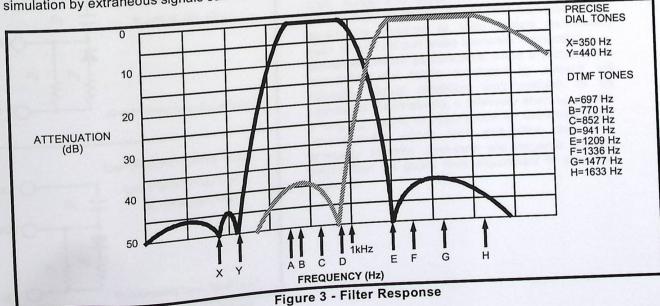

The telephone network is designed to carry voice signals, but the improvements in the telephone and cellular networks result in requirements to other types of signals. These signal used for user to interact with the phone company to set up a call or other services. It is also used in systems such as in voice mail, electronic mail and telephone banking.

Some type of these signals must exist in all generations of cellular systems as standards in telecommunication systems. One of these standards is Dual-tone multifrequency signal.

#### **Definition:**

DTMF signal: (Dual-tone multi-frequency) is a signal used in telephones and mobile for control features such as conference calling and call forwarding. This signal consists of the sum of two sinusoidal signals or frequencies appeared as a tune.

DTMF is the basis for voice communications control and is widely used worldwide in modern telephony to dial numbers and configure switchboards.

# **Generating DTMF signal**

When a user press a key from his mobile device a pair of frequencies will generate. These frequencies were chosen to prevent any Harmonics (no frequency is a multiple of another, the difference between any two frequencies does not equal any of the frequencies, and the sum of any two frequencies does not equal any of the frequencies) from being incorrectly detected by the receiver as some other DTMF frequency.

Each pair of tones contains one frequency of the:

- Low group (697 Hz, 770Hz, 852 Hz, and 941 Hz).

- High Group (1209 Hz, 1336 Hz, 1477Hz).

And represents a unique symbol. The frequencies allocated to the push-Buttons of the telephone pad are shown in the following table.

| High Low | 1209 HZ | 1336 HZ | 1477 HZ |

|----------|---------|---------|---------|

| 697 HZ   | 1       | 2       | 3       |

| 770 HZ   | 4       | 5       | 6       |

| 852 HZ   | 7       | 8       | 9       |

| 941 HZ   | *       | 0       | #       |

Table (2.2): frequencies allocated to the push-Buttons

There are four frequencies associated with the four rows, and three frequencies associated with the three columns.

Each key then specifies two frequencies. The DTMF signal for that key is the sum of two sinusoidal waves, one at each frequency.

For example, the digit '4' translates into a sound with two tones, one at 770 Hz. and the other at 1209 Hz.

The two frequencies are transformed to a DTMF signal using equation (1).

$F(t) = A_a \sin (2\pi f_a t) + A_b \sin (2\pi f_b t)$ (1)

Where:

$f_{a:}$  is the high frequency.  $f_{b:}$  is the low frequency.

Where the ratio between the two amplitudes should be:

$Ab / Aa = K \quad 0.7 < K < 0.9$  (2)

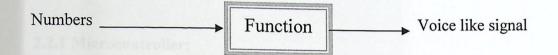

So the system is needed must generate an analog signal associated to a number this structure show in fig.2. 3. It converts sequences of numerical digits into signals that will easily traverse circuits designed for voice. The internationally standardized way to do that is DTMF signaling, or dual-tone, multi-frequency.

DTMF signaling converts decimal digits (and the symbols '\*' and '#') into sounds that share enough essential characteristics with voice to easily traverse circuits designed for voice.

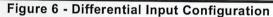

Figure (2.5) decoder function

#### **Receiving /Decoding the DTMF signal**

DTMF detection is used to detect DTMF signals in the presence of speech and dialing tone pulses.

The DTMF coding scheme ensures that each signal contains one and only one component from each of the high and low groups. This significantly simplifies decoding because the composite DTMF signal maybe separated with band pass filters, into its two single frequency components each of which may be handled individually.

Analog DTMF detection is done using band pass filter banks with center frequencies at the DTMF signal frequencies. Analog receivers have wide tolerances to compensate for distortion caused by aging transmitter variations in keying characteristics, and transmission line distortion. These distortions compound the problem of digital DTMF detection.

In digital switching systems is desirable to treat all signals uniformly, bringing all signals through A/D converters and switching them through the PCM system. Therefore the need for digital DTMF detection is justifiable to avoid the costs of hardware and D/A conversion needed to use analog detectors.

It is economically useful to replace analog detectors with their digital counterparts which are more reliable, maintenance cost effective, and spatially minimal. Several techniques for digital DTMF detection have been used, but most designers have settled on either digital filtering or discrete Fourier transform (DFT). In digital filtering, DTMF signals are passed through digital band pass filters centered at the signaling frequencies (shades of analog). The power at each frequency is then measured repeatedly to detect the DTMF tones.

The DTMF signaling frequencies are very closely spaced. It is obvious that the bandwidth of the filter used for detection must be narrow enough to avoid any bleeding of adjacent frequencies.

## 2.2 Hardware related to the project

Hardware components of the project are:

- 1. Microcontroller

- 2. Mobile Phone

- 3. Sensors

#### 2.2.1 Microcontroller:

A microcontroller is a cheap single chip microcomputer. Single-chip Microcomputer indicates that the complete microcomputer system lies within the confine of the integrated circuit chip. microcontrollers are capable of storing and running the program that was written, complied and downloaded into it. The main parts of a microcontroller generally consist of the central processing unit (CPU), random access memory (RAM), read only memory (ROM), input / output lines (I/O lines), serial and parallel ports, timers and other peripherals such as analog to digital (A/D) converters and digital to analog (D/A) converter.

#### 2.2.2 Sensors:

We classify sensors using two important functional axes: proprioceptive / exteroceptive and passive/ active.

Proprioceptive sensors measure values internal to the system exteroceptive sensors acquire information from the environment .passive sensor measure ambient environmental energy entering the sensor.

Active sensors emit energy into the environment, and then measure the environmental reaction.

#### 2.2.3 Mobile phone:

This device is used to transmit the SMS message and to receive the DTMF signal and forward it to next stages. And this phone must have some specifications like At command support that need it in the project.

#### **2.3 Project Integrity**

Our aim is to have a complete and integrated system at the end of this semester, so we will do our best to achieve this, our proposed design is to use the microcontroller to send a message when a sensor is triggered using the mobile

Many factors went into decision of finalizing our design, after gathering information about costs and communication between devices, we opted to start from a simple design, prototype it, and, after evaluation, if we feel confident about it we could improve it.

### 2.4 Theoretical Background about Project Components

In this section, we provide a full explanation of each component and each part of this project.

#### 2.4.1 PIC Microcontroller

A microcontroller is a high integrated chip which includes , on chip , all or most of the parts needed for a controller . The microcontroller could be called "one chip solution ".

#### PIC 16F877A features:

- 40-Pin Enhanced Flash Microcontrollers

- Analog Comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (VREF) module

- Programmable input multiplexing from device inputs and internal voltage reference

- Comparator outputs are externally accessible

Figure (2.6) 16f877A

#### 2.4.2 DTMF Decoder

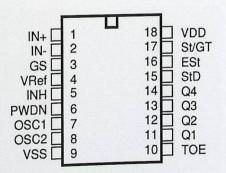

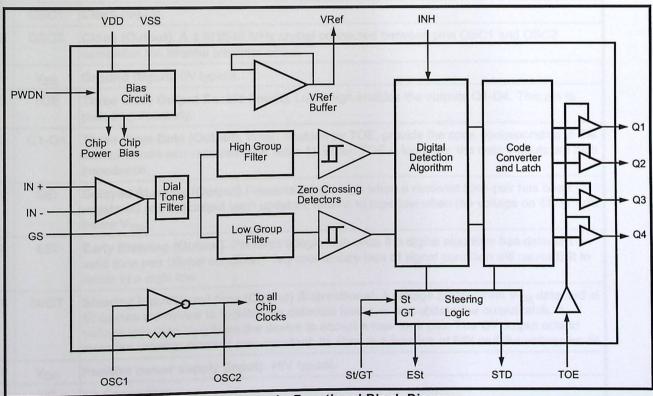

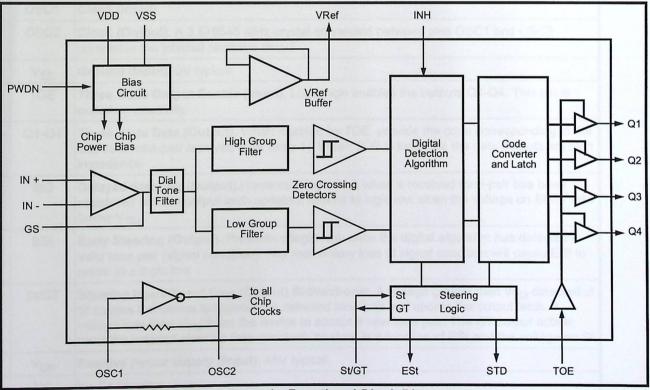

We will use a single chip (MT 8870) DTMF as decoder that receives and converts the DTMF signal to the corresponding binary pattern (4 bits). Table 3.2 shows MT8870 Output Truth Table.

| Key |   | 24 Q3 | 3 Q2 ( | Q1 |

|-----|---|-------|--------|----|

| 1   | 0 | 0     | 0      | 1  |

| 2   | 0 | 0     | 1      | 0  |

| 3   | 0 | 0     | 1      | 1  |

| 4   | 0 | 1     | 0      | 0  |

| 5   | 0 | 1     | 0      | 1  |

| 6   | 0 | 1     | 1      | 0  |

| 7   | 0 | 1     | 1      | 1  |

| 8   | 1 | 0     | 0      | 0  |

| 9   | 1 | 0     | 0      | 1  |

| 0   | 1 | 0     | 1      | 0  |

| *   | 1 | 0     | 1      | 1  |

| #   | 1 | 1     | 0      | 0  |

| A   | 1 | 1     | 0      | 1  |

| В   | 1 | 1     | 1      | 0  |

| С   | 1 | 1     | 1      | 1  |

| D   | 0 | 0     | 0      | 0  |

Table (2.3) MT8870 Output Truth table

This table dealing with 16-key devices that generate the DTMF signal.

As an example when the user press number 4 in his mobile he will generate a signal that converted to 0100 binary .Each bit in this pattern is an output of MT8870 pins.

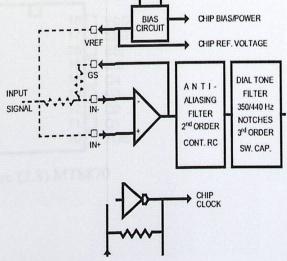

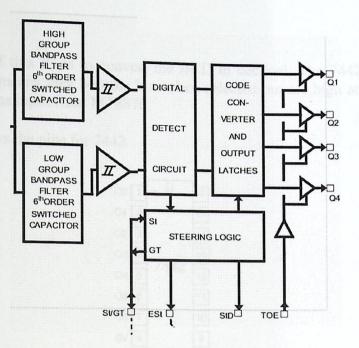

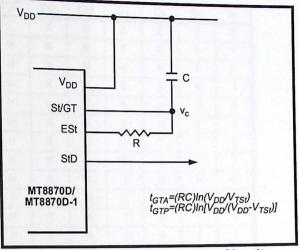

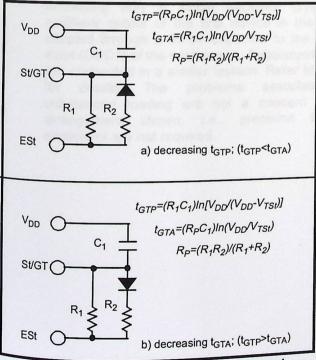

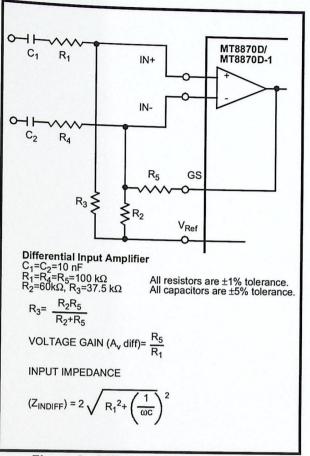

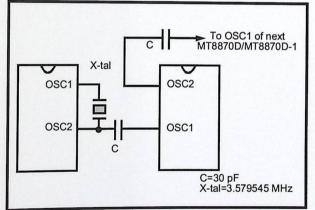

The MT8870 is a state of the art single chip DTMF receiver incorporating switched capacitor filter technology and a digital counting averaging algorithm for period measurement. The block diagram (Figure 3.4) illustrates the internal workings of this device.

Figure (2.7). (a) Input stage Inside MT8870 IC [4]

Figure (2.7). (b) Output stage Inside MT8870 IC [4]

たい そうない

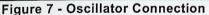

The DTMF input signal is first buffered by an input op-amp which allows adjustment of gain and choice of input configuration. The input stage is followed by a low pass continuous RC active filter which performs an antialiasing function. Dial tone at 350 and 440Hz is then rejected by a third order switched capacitor notch filter. The signal, still in its composite form, is then split into its individual high and low frequency components by two sixth order switched capacitor and pass filters. Each component tone is then smoothed by an output filter and squared up by a hard limiting comparator. The two resulting rectangular waves are applied to digital circuitry where a counting algorithm measures and averages their periods. An accurate reference clock is derived from an inexpensive external 3.58MHz color burst crystal.

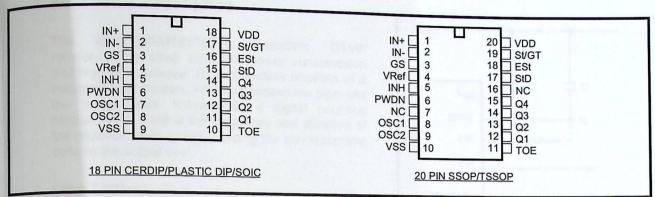

The following figure shows the pins for MT8870

Figure (2.8) MT8870

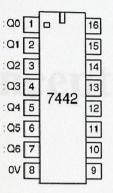

#### 2.4.4 IC 7442:

The function of this IC is to convert the BCD to decimal. The 7442 outputs are active-low which means they become low when selected but are high at other times. We will use 4 pin as input from MT8870.

Figure 2.9 shows the pins for 7442

#### Figure (2.9) IC 7442

「おおいま」、「おい

Wenisser Beales Block Diserces

Product Information with the Serroueting Environment

To Besteine Mandola

# **CHAPTER THREE**

# 3

# **Project Conceptual Design**

- 3.1 Project Objectives.

- 3.2 Design Realization Approach

- 3.3 Project Design Block Diagram

- 3.4 Project Interacting with the Surrounding Environment

- 3.5 System Models

The following figure shows the black diagrams of our system. It consists of several south are accomplished and integrand to form the linal scourty system black series are

L. Call Madale

Defections while contribute different sensors to detect movement of a pro-

contents a FIC must controller and a Fig

- Sorbal Compections

#### Introduction:

In this chapter, we are going to describe the detailed objectives of the system the general block diagram and explain how the system works.

#### 3.1 Project Objectives

This project supports many ideas and objectives that can be summarized as follows:

- 1. Processing the tune frequencies that generated by key pressing from mobile to other signals by using specific decoder.

- 2. Develop a receiver system using a per mobile.

- 3. To design a security system for a car.

- 4. Design a system that can dial a number.

#### **3.2 Design Realization Approach**

One of the most complicated parts to decide on is how to apply our idea of project on the real world many approaches was used.

語を、語の語のです。

Fortunately, all the needed chips were available with a reasonable price so there were no problems to get them and to start the hardware implementation.

#### 3.3 Project Design Block Diagram

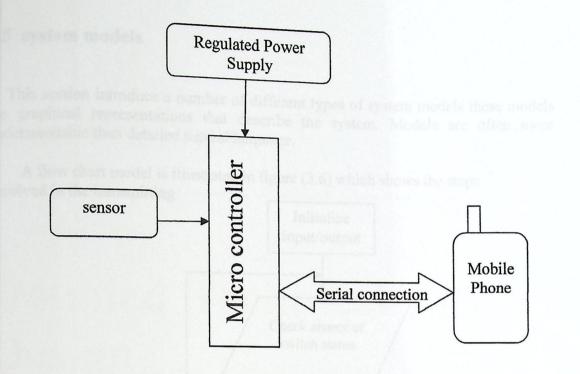

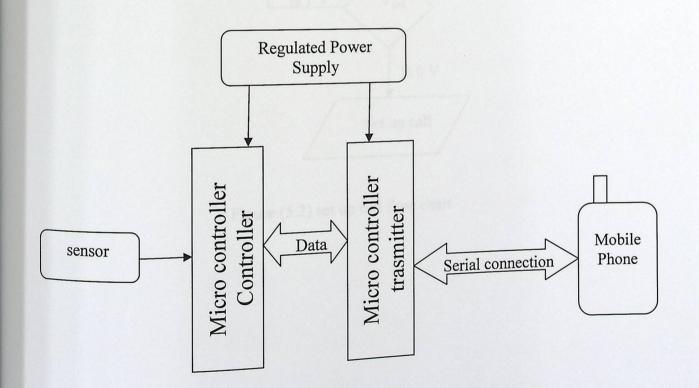

The following figure shows the block diagrams of our system. It consists of several units are accomplished and integrated to form the final security system these units are:

#### 1. Call Module

#### • Detection unit:

This contains different sensors to detect movement of a person.

#### Transmitter unit •

This contains a PIC microcontroller and a mobile

#### Serial Connection:

1111

#### 2. DTMF Module

- Receiver unit : which is a mobile

- Decoder

Figure (3.2) DTMF Module

# 3.4 Project Interacting with the Surrounding Environment

When someone break into the car the sensor will send a signal to the PIC which will setup a call using the mobile connected to it. Then the user can disrupts the working of the engine.

#### 3.5 system models

This section introduce a number of different types of system models these models are graphical representations that describe the system. Models are often more understandable than detailed natural language.

A flow chart model is illustrated in figure (3.6) which shows the steps Involved in the transmitting

# **CHAPTER FOUR**

# **Detailed Technical Project Design**

4.1 Detailed Description of the Project Phases

4.2 Overall Systems Design

#### Introduction:

After explaining the theoretical background, the general block diagram of the system, and how the system works, there is a need to view what is the design of this system in more specific, powerful and more formal terms .this chapter describes the detailed system design with all its features that are necessary to make the system works well.

## 4.1 Detailed Description of the project phases

The detailed description of the project phases as follows:

#### • Sensory Phase :

Sensor used to gather the status of the surrounding environment. We will use sensor that be hold on the car so any one sit down will trigger a high voltage whenever anyone try to steal the car.

#### • Processing Phase :

A PIC microcontroller is used to continuously check the status of the sensor .then, based on that it will produce the appropriate code to be sent, so it's needed to combine signals from various sensors.

• Transmitter phase :

When the sensor is trigged the PIC will serially communicate with the Mobile which will send the alarm message.

• Receiving phase :

The receiver of the alarm will be the mobile of a number that we program it on the PIC microcontroller .in the other hand when we want to shut down the car we will use the DTMF and a peer mobile in the receiver.

## 4.2 Overall System Design

In this section the schematics, characteristic, features, and the specifications Of each component and subsystem will be presented.

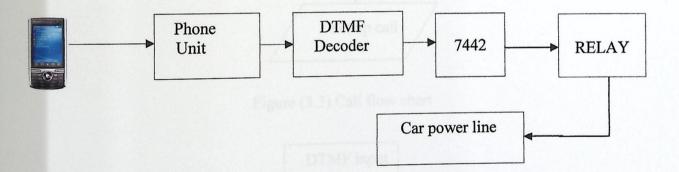

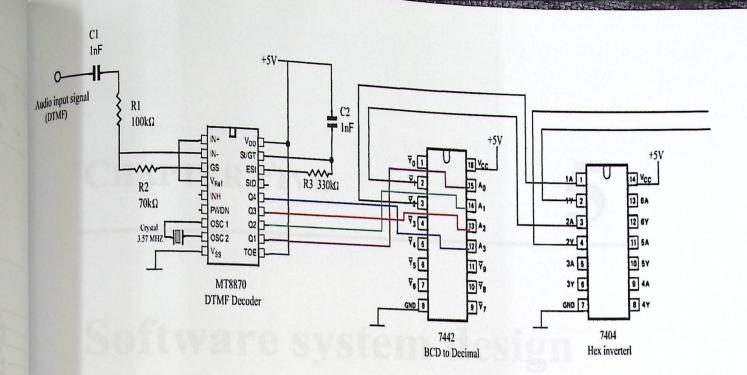

Figure (4.2) DTMF circuit

This circuit schematic shows the main component in DTMF receiver which are listed as follow:

#### 1. MT 8870:

We will use a single chip (MT 8870) DTMF as decoder that receives and converts the DTMF signal to the corresponding binary pattern (4 bits

#### 2. 7442:

The function of this IC is to convert the BCD to decimal. The 7442 outputs are active-low which means they become low when selected but are high at other times. We will use 4 pin as input from MT8870.

#### 3. Relay

Is an electromagnetic operated switch that connect two different circuits. Table 3.3 shows the relay pins.

|   | (Common)           |

|---|--------------------|

|   |                    |

|   | (Normally Open)    |

| - | (Normally Closed)  |

|   |                    |

|   | Drive Voltage      |

|   | Number of Contacts |

|   | Number of Contacts |

|   | Contact Capacity   |

|   | Contact Capacity   |

Table 4.1 the relay pins

1. 1. 1. 1.

# **CHAPTER FIVE**

Software system design

- 5.1 Software needed for the project.

- 5.2 How software system works.

- 5.3 Code listing.

#### Introduction:

This chapter talks about implementing the system from a programming point of view. This includes the code, the algorithms used in the system and flow charts That explains the sequence of all the stages of the programs.

## 5.1 Software needed for the project

PIC programmer was used to program the PIC 16F877. Program written in Assembly language must be translated into "hex code" in order for a microcontroller to understand it ." Assembly language "and "assembler "are two different notions. The first represents a set of rules used in writing a program for a microcontroller and the other is a program on the personal computer which translate assembly language into zeroes and ones .physically, program represents a file on the computer disc (or in the memory if it is read in the microcontroller), and is written according to the rules of assembler or some other language for microcontroller programming translator interprets each instruction written in assembly language as a series of zeroes and ones which have a meaning for the internal logic of the microcontroller.

Figure (5.1) represents all the phases of programming of the PIC.

# 5.2 How system software works

In this section, flowchart will be introduced to describe the programs of both The PIC, flowcharting is a tool for analyzing process.

# 5.3 code listing

## 5.3.1 Controller Pic

#include "p16f877a.inc" PROCESSOR 16f877a

# \_\_\_\_\_CONFIG \_\_DEBUG\_OFF & \_CP\_OFF & \_PWRTE\_ON & \_BODEN\_ON & \_\_\_\_\_XT\_OSC & \_\_WDT\_OFF & \_LVP\_OFF

| BOOLEAN  | equ      | 0x20          |

|----------|----------|---------------|

| tmp1     | equ      | 0x21          |

| tmp2     | equ      | 0x22          |

| tmp3     | equ      | 0x23          |

| tmp4     | equ      | 0x24          |

| tmp5     | equ      | 0x25          |

| tmp6     | equ      | 0x26          |

| rut_DAT  | equ      | 0x27          |

| rut_TMP1 | equ 0x28 |               |

| #define  | portDAT  | TRISB, 4      |

| #define  | DAT      |               |

| #define  | CLK      |               |

| #define  | Ι        |               |

| #define  | Н        |               |

| BANK0    | MACRO    | am I MIIG DD1 |

|          | bcf      | STATUS, RP1   |

|          | ; BANK 0 | GTATIC DDO    |

|          | bcf      | STATUS, RP0   |

|          | ENDM     |               |

| BANK1    | MACRO    | STATUS, RP1   |

|          | bcf      | STATUS, MT    |

|          | ; BANK 1 | STATUS, RP0   |

|          | bsf      | STATUS, IL C  |

|          | ENDM     |               |

| BANK2    | MACRO    | STATUS, RP1   |

|          | bsf      | 5111102,-     |

|          | ; BANK 2 | STATUS, RP0   |

|          | bcf      | Dirice        |

|          | ENDM     |               |

| BANK3    | MACRO    | STATUS, RP1   |

|          | bsf      |               |

|          | ; BANK 3 | STATUS, RP0   |

|          | bsf      |               |

| NDM      |          |               |

|          |          |               |

| PAGEO    | MACRO    | PCLATH,       |

| - TOLO   | BCF      |               |

|          | BCF         |                 |          |

|----------|-------------|-----------------|----------|

|          | ENDM        | PCLATH, 4       | main     |

| PAGE1    | MACRO       |                 |          |

|          | BSF         |                 |          |

|          |             | PCLATH,         | 3        |

|          | BCF         | PCLATH,         |          |

| PAGE2    | ENDM        | ,               | •        |

| FROD     | MACRO       |                 |          |

|          | BCF         | PCLATH,         | 2        |

|          | BSF         | PCLATH,         |          |

|          | ENDM        |                 | •        |

| PAGE3    | MACRO       |                 |          |

|          | BSF         | PCLATH,         | ,        |

|          | BSF         | D CT            | 3        |

|          | ENDM        | ICLAIR, 2       | 4        |

|          | ORG         | 00000           |          |

|          | bcf         | 0x0000          |          |

|          | bcf         |                 | 3        |

|          |             | PCLATH,         | 4        |

|          | nop         |                 |          |

| T '4     | GOTO Init   |                 |          |

| Init     | BANK1       |                 |          |

|          | bel a       |                 |          |

|          | movlw b'000 |                 |          |

|          | movwf ADC   | ON1             |          |

|          |             |                 |          |

|          | clrf OPTI   | ON_REG          |          |

|          |             |                 |          |

|          | movlw b'111 | 11000'          |          |

|          | movwf TRIS. | A               |          |

|          | movlw b'010 |                 |          |

|          | movwfTRIS   |                 |          |

|          | movlw b'101 |                 |          |

|          | movwfTRIS   | C               |          |

|          | movlw b'111 | 11111'          |          |

|          | movwfTRIS   | D               |          |

|          | movwi TKIS  | 11111'          |          |

|          | movlw b'111 |                 |          |

|          | movwfTRIS   | Е               |          |

|          |             |                 |          |

|          | BANK0       | TT.             |          |

|          | bsf         | Hx              |          |

|          |             |                 |          |

|          | clrftmp1    |                 |          |

|          | decf tmp1   | , 1             |          |

|          |             |                 | ot zero  |

|          | btfss STAT  | TUS,Z ; do if r | 101 2010 |

|          | GOTO \$-3   |                 |          |

|          |             |                 |          |

|          | alaf BOO    | LEAN            | labra    |

|          | DOD'        | ГА              | ; debug  |

|          | clrf POR    |                 |          |

| leds off |             |                 |          |

| The OIL  |             |                 |          |

|          | BCF                   | DCT A man          |             |

|----------|-----------------------|--------------------|-------------|

| CF1      | ENDM                  | PCLATH,            | 4           |

| PAGE1    | MACRO                 |                    |             |

|          | BSF                   | PCLATH,            |             |

|          | BCF                   | PCLATH,<br>PCLATH, | 3           |

| DACE?    | ENDM                  | ICLAIR,            | 4           |

| PAGE2    | MACRO                 |                    |             |

|          | BCF                   | PCLATH,            | 3           |

|          | BSF                   | PCLATH,            | 4           |

| DACE2    | ENDM                  | ,                  | -           |

| PAGE3    | MACRO                 |                    |             |

|          | BSF                   | PCLATH,            | 3           |

|          | BSF                   | PCLATH,            | 4           |

|          | ENDM                  |                    |             |

|          | ORG                   | 0x0000             |             |

|          | bcf                   | PCLATH,            | 3           |

|          | bcf                   | PCLATH,            | 4           |

|          | nop                   |                    |             |

|          | GOTO Init             |                    |             |

| Init     | BANK1                 |                    |             |

|          | 1 1.00                |                    |             |

|          | movlw b'00            |                    |             |

|          | movwfAD               | CONI               |             |

|          |                       | TION DEC           |             |

|          | clrf OP'              | TION_REG           |             |

|          | 1 1/1:                | 11110001           |             |

|          | movlw b'1             |                    |             |

|          | movwfTR               |                    |             |

|          | movlw b'0             |                    |             |

|          | movwfTR               |                    |             |

|          | movlw b'10            |                    |             |

|          | movwf TR<br>movlw b'l | 11111111           |             |

|          | movwfTR               | ISD                |             |

|          | movwr r<br>movlw b'1  | 11111111           |             |

|          | movwfTR               | ISF                |             |

|          | movwillk              | 191                |             |

|          | DANKO                 |                    |             |

|          | BANK0                 | Hx                 |             |

|          | bsf                   |                    |             |

|          | 1-ftmn1               |                    |             |

|          | clrftmp1<br>decf tmj  | 51, 1              |             |

|          |                       |                    |             |

|          | btfss ST.             | ATUS,Z ;do         | if not zero |

|          | GOTO \$-3             |                    |             |

|          |                       |                    |             |

|          | clrf BC               | OLEAN              | ; debug     |

|          | clrf PO               | RTA                | , 00005     |

|          | UIII                  |                    |             |

| leds off |                       |                    |             |

|          |                       |                    |             |

Sec. 1