# **Palestine Polytechnic University**

College of Engineering & Technology Electrical and Computer Engineering Department Biomedical Engineering

**Graduation Project**

**Experimental Board for Biomedical laboratory**

Project Team

Yousef Al-Aloul

**Bashar Al-Trawa**

Raid Abu-Na'meh

**Project Supervisor**

Eng. Abdullah Erman

Hebron – Palestine July ,2004

# **Palestine Polytechnic University**

College of Engineering & Technology Electrical and Computer Engineering Department Biomedical Engineering

**Graduation Project**

**Experimental Board for Biomedical laboratory**

Project Team

Yousef Al-Aloul

**Bashar Al-Trawa**

Raid Abu-Na'meh

**Project Supervisor**

Eng. Abdullah Erman

**Hebron – Palestine**

July ,2004

# **Experimental Board for Biomedical laboratory.**

By

Bashar Al-Trawa Yousef Al-Aloul Raid Abu Na'meh .

According to the direction of the supervisor and by agreement all of the committee member ,this project submitted to department of electrical and computer in college of engineering and technology to partially fulfill to the bachelor requirement for the department .

| Supervisor signature | Dept .Head Signature |

|----------------------|----------------------|

| Name:                | Name:                |

### Abstract

#### **Experiment Board for Biomedical laboratory.**

By Bashar Al-Trawa Yousef Al-Aloul Raid Abu-Na'meh

#### Palestine polytechnic university – 2004

Supervisor

Eng. Abdullah Erman

In this project we will design and implement an experimental board for the biomedical laboratory .It includes circuits as (op amp, instrument rectifier ,low pass filter, high pass filter, comparator-Schmitt trigger ,negative impedance converter ,gyrator )and bridge circuits as inputs to sensors such as (temperature ,phototransistor, pressure, etc...).With A/D converter and D/A converter.

على بناء لوحة لتجارب تستخدم في مختبر الأجهزة الطبية تتضمن الدوائر الإلكترونية ( تشغيلية . . مرشح ترددات منخفضة نوعيه نشطه . ترددات مرتفعه نوعيه نشطه ـ . محول المقاومة الكهربائيه دارة جايريتر) ضافة إلى المجسات (حراري – \_ )التي تكون ضمن قنطرة وتستوون بالإضافة إلى محول أشارة مستمرة/رقمية ورقمية/

# Dedication

To our parents ... To our families ... To our country ... To our supervisor Eng. Abdullah Erman ... To our friends and any one who loves us ...

Bashar & Yousef & Raeid

# Acknowledgments

We would like to thank our families and our friends for their support and encouragement through our study.

Also ,we would like to thank our supervisor Eng. Abdullah Erman for his efforts and his notes.

# Table of contents

| Title Page                              | i   |

|-----------------------------------------|-----|

| Project title and supervisor signatures | ii  |

| Abstract                                | iii |

| Dedication                              | iv  |

| Acknowledgements                        | v   |

| Table of contents                       | vi  |

| List of tables                          | ix  |

| List of figures                         | Х   |

# **Chapter One**

| 1.1 Project Overview | 2 |

|----------------------|---|

| 1.2 Time plan        | 3 |

| 1.3 Report Contents  | 5 |

# **Chapter Two**

| 2.1 Introduction                                   | 7  |

|----------------------------------------------------|----|

| 2.2 sensor unit ( U1)                              | 7  |

| 2.3 Measurement of instrumentation                 | 8  |

| 2.4 Sensors and transducers                        | 9  |

| 2.4.1 Photosensor                                  | 10 |

| 2.4.2 Temperature sensors                          | 12 |

| 2.4.2.1 Thermoresistive sensor                     | 12 |

| 2.4.2.2 Thermistor (thermally sensitive resistor ) | 13 |

| 2.5 Whetstone bridge                               | 14 |

# **Chapter Three**

| 3.1 Bioelectric amplifie | r | 18 |

|--------------------------|---|----|

| 3.2 Amplifier circuits   |   | 20 |

| 3.2.1 The operation amplifier: ideal op-amp model | 21 |

|---------------------------------------------------|----|

| 3.2.2 Open loop gain                              | 23 |

| 3.2.3 Closed loop gain                            | 23 |

| 3.2.4 Common Mode Rejection ratio                 | 24 |

| 3.2.5 Bias and offset                             | 25 |

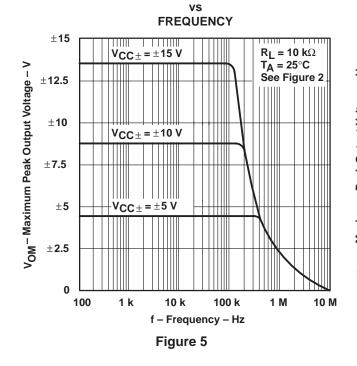

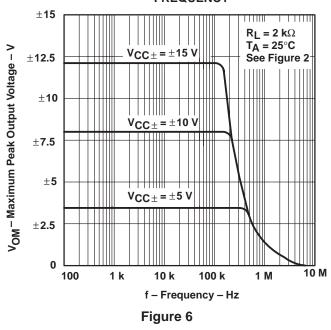

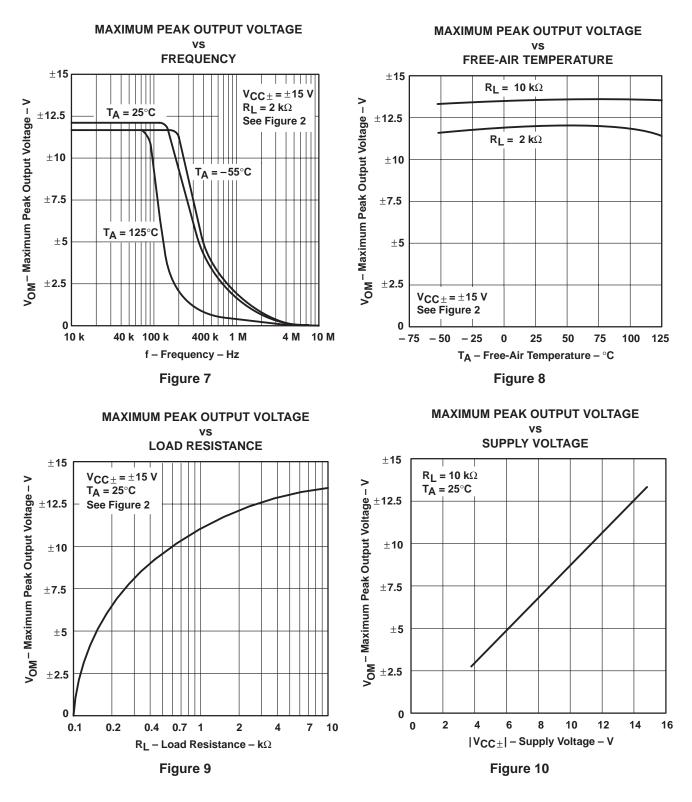

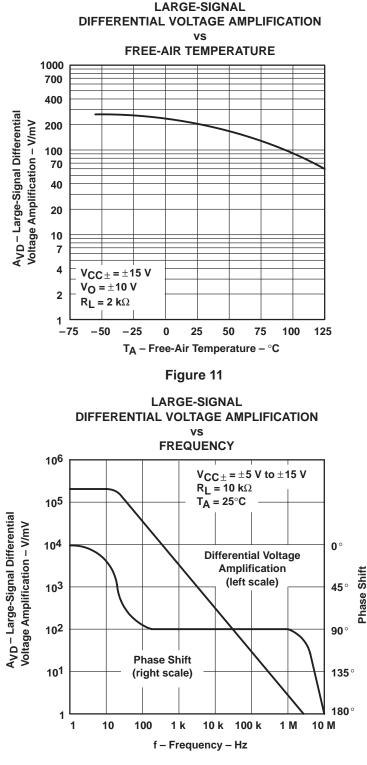

| 3.2.6 Frequency response                          | 25 |

| 3.2.7 Slew rate                                   | 26 |

| 3.3 Instrumentation amplifier                     | 28 |

| 3.4 Filters                                       | 30 |

| 3.4.A passband and stopband attenuation           | 31 |

| 3.4.BApproximation response                       | 32 |

| 3.4.B1 Butterwort approximation                   | 32 |

| 3.4.B2 Chebysheyev approximation                  | 33 |

| 3.4.B3 Inverse chebysheyev approximation          | 33 |

| 3.4.B4 Elliptic approximation                     | 34 |

| 3.4.B5 Bessel approximation                       | 34 |

| 3.4. low pass filter                              | 34 |

| 3.4.1.1 first order Low-pass filter               | 35 |

| 3.4.1.2 low pass filter second order              | 37 |

| 3.4.2High pas filter                              | 39 |

| 3.4.2.1 High pass filter first order              | 40 |

| 3.4.2.2 high pass filter second order             | 41 |

| 3.5 Comparator                                    | 42 |

| 3.6 Active rectifier                              | 44 |

| 3.7 Negative impedance converter and gyrator      | 46 |

| 3.7.A NIC circuits                                | 46 |

| 3.7.B Gyrator                                     | 48 |

| 3.8 Data conversion unit (U3)                     | 50 |

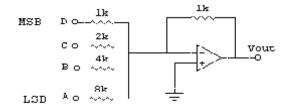

| 3.8.1 Digital to analog converter (D\ Ac)         | 52 |

| 3.8.2 Analog to digital signal A/Dc | 53 |

|-------------------------------------|----|

| Chapter four                        |    |

| Testing                             | 56 |

| Chapter five                        |    |

| Conclusion and Future work          |    |

| References                          | 65 |

| Appendix                            |    |

| Appendix A                          | 67 |

| Appendix B                          | 68 |

# List of the Tables

| Tables (1.1) Time Scheduling in First Semester    | 4 |

|---------------------------------------------------|---|

| Tables (2.1) The Type energy and their Occurrence | 9 |

# List of Figures

| Figure (2.1): sensor unit U1                           | 7  |

|--------------------------------------------------------|----|

| Figure (2.2) General block diagram for the system      | 8  |

| Figure (2.3) Wheatstone bridge                         | 15 |

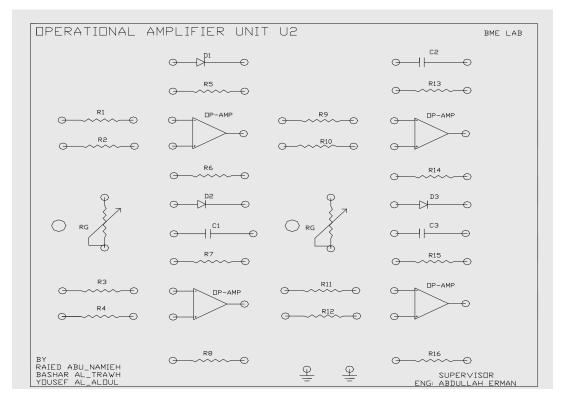

| Figure (3.1): operational amplifier unit U2            | 17 |

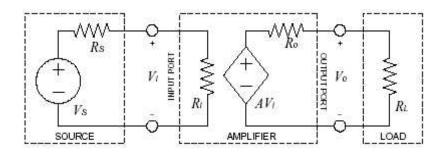

| Figure (3.2) Circuit model for an amplifier circuits   | 21 |

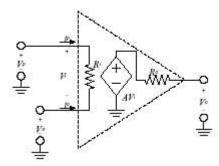

| Figure (3.3) Standard operation amplifier              | 21 |

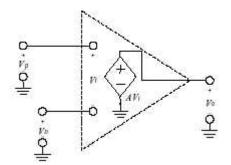

| Figure (3.4) Ideal operation amplifier                 | 21 |

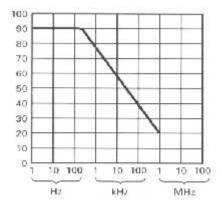

| Figure (3.5) Frequency response                        | 24 |

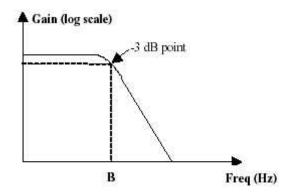

| Figure (3.6) Frequency response of operation amplifier | 26 |

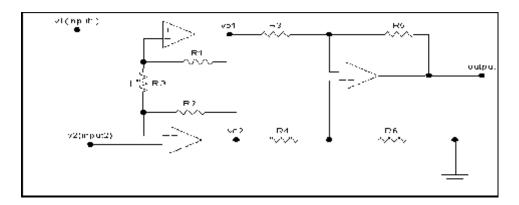

| Figure (3.7) Instrumentation amplifier                 | 29 |

| Figure (3.8) Realistic low pas filter                  | 32 |

| Figure (3.9) Ideal low pass response                   | 34 |

| Figure (3.10) First order low pass filter              | 35 |

| Figure (3.11) Second order low pass filter             | 37 |

| Figure (3.12) Ideal high pas response                  | 39 |

| Figure (3.13) First order high pass filter stages      | 40 |

| Figure (3.14) Second order high pass filter            | 41 |

| Figure (3.15) ideal Comparator                         | 42 |

| Figure (3.16) Schmitt trigger                          | 43 |

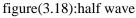

| Figure (3.17) full wave                                | 44 |

| Figure (3.18) Half wave                                | 44 |

| Figure (3.19) Half wave rectifier                      | 45 |

| Figure (3.20) Full wave rectifier                      | 46 |

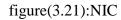

| Figure (3.21) Negative impedance coverer               | 47 |

| Figure (3.22) Gyrator                                  | 48 |

| Figure( 3.23): generalized impedance converts          | 48 |

| Figure (3.24) data conversion unit                     | 51 |

| Figure (3.25) A/Dc to D/Ac process | <br>52 |

|------------------------------------|--------|

| Figure(3.26)D/Ac summing amplifier | <br>53 |

# **Chapter One**

1.1Project Overview1.2Time plan1.3 Report contents

## **Chapter One: Introduction**

#### **1.1Project Overview:**

To cope with the development of technology and science in the fields that involve human beings and health care, new branch of science has emerged to the surface dealing with the biomedical instruments. This science is called the Biomedical Engineering.

The biomedical instrument is an electric device that has outputs and sensors. Biomedical instruments are very important in medicine and health fields. Through these instruments, we can examine and diagnose the state of various patients, give them treatment, and put them under continuous observation.

The biomedical engineering lab is considered the backbone for this field. It gives and supports the students with theoretical and practical information about biomedical instruments by using modern boards. These boards are comprehensive and powerful learning tools that help student study sensors and electronic circuits. These boards are used for the application of the experiments. The main purpose of each experiment is to familiarize students with the general principle involved in practical application and to achieve great understanding.

In this project we will introduce one of these equipments that supports our lab with additional sensors and experimental board coverage of fundamental modern instruments. This board consists of three units. Each unit has been carefully selected to fulfill the practical experience requirements. The first unit is the input sensor unit (U1). This unit contains the signal detecting bridge that accepts any type of sensors.

The second unit is the operational amplifier unit (U2). This unit consists of separated op-amp with resistances diodes and capacitors. They can connect whatever needed from processing: (op-amp (inverting and noninverting), instrumentation amplifier, comparators (Schmitt Trigger), low pass filter-high pass filter, instrument rectifier, and negative impedance convert (NIC). The third unit is data conversion unit (U3). It is a signal converter that is divided into A/D converter and D/A converter sections which can give us the output by indicator LEDs.

#### Project Cost:

- Equipment cost: It included the cost of main components of the project. Here, we list the main parts and the approximate cost of each part:

- $\circ$  Electronic pieces (40 \$).

- o A/Dc D/Ac (10 \$).

- Board printing (20 \$).

- Other electrical and mechanical components (40 \$).

- Additional cost (50 \$).

#### *Total* = 160 \$

• Project team expenses: It includes all the miscellaneous expenses required by the project team to accomplish this project. These costs are invaluable.

### 1.2Time plan:

The time period given to accomplish the work in this project is limited to two semesters, 15 weeks each .this section shows an illustration to the time plan which applied through the different stage to accomplish the work in the project. In the first semester, the work is divided into eight tasks are the following:

1. Selecting the project idea.

- 2. Discussing the idea.

- 3. Requirement analysis.

- 4. Gathering information related to the project.

- 5. Primary design.

- 6. Hardware system design.

- 7. Report documentation.

| week           | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|----------------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| task           |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

| Selecting the  |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

| project        |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

| Discussing the |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

| idea           |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

| Requirement    |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

| analysis       |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

| Gathering      |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

| information    |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

| primary        |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

| design         |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

| Hardware       |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

| design         |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

| Report         |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

| documentation  |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

Table1.1: Time scheduling in first semester.

In the second semester ,we began the real implementation of system .this work is also divided into 15 weeks .the main stages of our work at this period include:

- 1. Buying the components.

- 2. Building the boards units.

- 3. Testing.

# **1.3 Report contents:**

The report is divided into five chapters; these chapters are described as follows:

Chapter one: Introduction.

<u>Chapter two:</u> this chapter illustrates the general block diagram and input stage which contain sensors types and how connect to Whitestone bridge.

<u>Chapter three:</u> contains of the detail system hardware components(op amp ,instrumentation amplifier, instrument rectifier, Schmitt trigger comparator ,low pass filter ,high pass filter, negative impedance converter, gyrator , D/Ac , A/D converters)

<u>Chapter four:</u> this chapter describes the testing process by showing testing stages by details .

<u>Chapter five:</u> conclusion and future work.

# **Chapter Two**

- **2.1 Introductions**

- 2.2 sensor unit (U1)

# 2.3 Measurement of instrumentation

- 2.4 Sensors and transducers

- 2.5 Wheatstone bridge

# **Chapter Two**

# **2.1 Introductions**

This chapter describe sensor unit (U1), then we talk about some kind of biomedical sensors as application for our projects and describe the Wheatstone bridge circuits which we will use it in the Biomedical transducers.

# 2.2 sensor unit (U1):

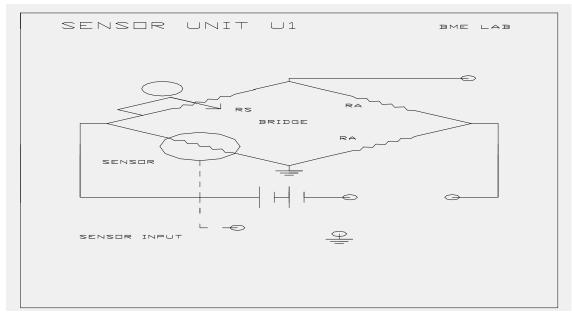

The sensor unit shown in figure (2.1) contain the signal detecting bridge circuits , the bridge inside unit is a resistor bridge , and accepts any type of sensors which presents resistance changes as the results of the sensing .

Figure (2.1): sensor unit U1

### 2.3 Measurement of instrumentation:

A measuring system is required to compare a quantity with a standard or to provide an output that can be related to the quantity being measured. The quantity to be measured is detected by the input sensor. The detected quantity may be converted to a mechanical form or electrical form of energy. For most biomedical purposes, the form is electrical . The measurement is greatly increased when all factors the measurement are understood. This requires a detailed knowledge of the measurement process and the possible interactions of the measurement process on the system being measured.

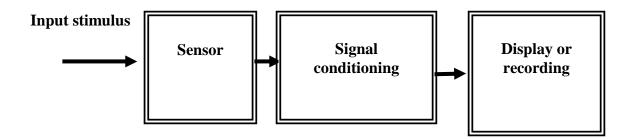

Most instrumentation systems comprise three basic general sections :one for sensing the measured ,the next for conditioning the sensed signal and finally one for displaying or recording the conditioned signal figure (2.2):

Figure(2.2): block diagram for experimental board system

### 2.4 Sensors and transducers:

The sensor and transducer are referring to measurement systems. transducers are electromechanical devices that convert a change in a mechanical quantity such as displacement or force into a change in an electrical quantity that can be monitored as a voltage after signal processing. A wide variety of transducers are available for use mechanical quantities. Transducer characteristics are determined primarily by sensor that is incorporated into the transducer to produce the electrical output.

A sensor is a device that detects a change in a physical stimulus and turns it into a signal which can be measured or recorded, normally, the sensor is just the sensing element itself.

Sensors classified according to the physical property that they use (piezoelectric, photovoltaic, etc.) or according to the function that they perform (measurement of length, temperature, etc.). Since energy conversion is an essential characteristic of the sensing process, the various forms of energy should be considered. The following table lists the main forms of energy and their occurrence:

| Types of energy | occurrence                            |

|-----------------|---------------------------------------|

| electrical      | Electric fields, currents             |

| magnetic        | Magnetic fields                       |

| thermal         | Kinetic energy of atoms and molecules |

| mechanical      | Motion, displacement, forces          |

Table(2.1): the types energy and their occurrence

# 2.4.1 Photosensors:

Photosensors are electronic control units that automatically adjust the output level of electric lights based on the amount of light detected. Lighting control devices enable occupants to control their lighting environment by either dimming the lights or switching them on and off. Some control devices, such as light switches, manual dimmers, and window blinds, can be directly accessed and controlled by occupants. Others, such as occupancy sensors, timers, and photo sensors, often are designed to take the place of occupant actions.

Photosensors are a form of automatic control that replaces or accompanies occupant control. The main reason for installing control devices is to conserve energy by switching off or dimming the electric lights when full output is not needed. The benefit of automatic control is that energy savings can occur throughout the day without human intervention. When combined with dimming electronic ballasts, photosensors can dim lights based on the amount of daylight entering a room. Problems easily arise, however, when occupants are disturbed by insufficient illumination levels or by sudden light level fluctuations. Meeting the occupants' visual and comfort needs as well as their expectations about good lighting is of primary importance for automatic lighting controls.

Photosensor respond to incident light energy, and produces an electrical signal as a result. The strength of the output signal is proportional to the intensity of the light. Some photosensor have built in light transmitters and receives. Photosensor can be

classified in terns of an optical, infrared, or a laser sensor depending upon the wavelengths of the light energy utilized.

### 2.4.1 LEDs and phototransistor:

Infrared LED and a receiver transistor in object detection. Two methods are use: In the first method, the transmitted light signal from the source is interrupted by the object. Therefore , the detection of an object is represented by non-existence of the light energy at the receiver(phototransistor).in contrast, the second method is based on the existence of the light signal at the receiving end that means the light source and receiver are arranged in such a way that the reflection from the object reaches the receiver.

#### Parameters characterize photo detection technique:

. **Light sensitivity**: the sensitivity depends on the distance between the source and object as well as the sensitivity of the receiver.

• **Response time**: a filament type lamp has a time delay due to the time taken in heating, or cooling the filament. In contrast, a semiconductor based light source response much faster when the energy source is turned on and off.

.wavelengths: normally, photosensor react to wavelengths of 751-950nm

the input voltage and light output of a light source has a linear relationship within the limit.

.photosensor should be isolated from unwanted lights.

### 2.4.2 Temperature sensors

### 2.4.2.1 Thermoresistive sensors

Thermoresistive sensors Based on materials whose resistance changes in accordance with temperature, from this type the following Resistance Temperature Detectors (RTDs) the material is metal (platinum, nickel, copper) are typically used, and has positive temperature coefficients (PTC), which mean; the resistance of RTDs increases as temperature increases, and decreases as temperature decreases.

$Rt=R0 [1+ 1T + 2T^{2} + 3T^{3}+...+ nT^{n}]....2.1$

Take only the first two terms and ignore the other terms from the above equation then Rt become as below.

Rt=R0 [1+ 1T].....2.2

Where:

Rt = RTDs resistance.

T = absolute temperature in Kelvin's.

= material constant for RTDs.

To = standard reference temperature (K).

#### 2.4.2.2 Thermistor (thermally sensitive resistor):

It is a thermoresitive sensor, which based on material whose resistance changes in accordance with temperature. Thermistor is a semiconductor material composes of a ceramic and metallic oxide (Mn, Co, Cu or Fe), and have negative temperature coefficient (NTC), which means (the resistance of thermistors decreases as temperature increases, and increases as temperature decreases).

#### **Specifications of thermistor:**

1. Resistivity used for biomedical applications is between 0.1-100 .m.

2.Small in size (they can be made less than 0.5 mm in diameter).

3.Large sensitivity to temperature changes (-3 to -5%/C).

4. Excellent long-term stability characteristics ( $\pm 0.2\%$  of nominal resistance value

per year.

$Rt = Roe^{-1} [ (To-T)/TTo] .....2.3$

#### Where

Rt = thermistor resistance.

T = absolute temperature in Kelvin's.

= material constant for thermistor it is usually 4000k.

To = standard reference temperature (K).

Sensitivity of Thermistor: sensitivity of an instrument determines how small a variation of a parameter can be reliably measure.

The definition of the temperature coefficient as a fractional change in resistance per unit change in temperature produces a result in which the fractional change in voltage per unit change in temperature is given by alpha as well.

$$sensitivity = \frac{dR}{dT}$$

.....2.4

$$\frac{dR}{dt} = \left(-\frac{B}{T^2}\right) \times Rt....2.5$$

### 2.5 Wheatstone bridge:

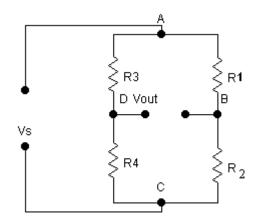

Many biomedical transducers are use in a circuits configuration called a Wheatstone bridge The basic form of Wheatstone bridge has a d.c. supply and each arm is a resistance see figure (2.3). The resistances in the arms of the bridge (R1, R2, R3, andR4) are so adjusted that the output potential difference Vo is zero. In this condition the bridge is said to be balanced. When the output potential difference is zero then the potential at B must equal that at D. This means that the potential difference across R1 (VAB) must equal that across R3 (VAD), I1 pass through R1, I2 pass through R3.

I1R1 = I2R3 .....2.6

It also means that VBC must equal VDC .Since there is no current through BD then the current through R2 must be I1 and that through R4 must be I2 .Thus

I1R2 = I2R4 .....2.7

Hence

$I1R1 = I2R3 = (I1R2/R4) R3 \dots 2.8$

R1/R2 = R3/R4 .....2.9

Figure(2.3) : Whetstone Bridge

The balance condition is independent of the supply voltage .it depends only on the resistances in the four bridge arms .If R2 and R4 are known fixed resistances from about 10hm to 1megaohm .The accuracy is determined by the accuracy of the known resistors and the sensitivity of the null detector .

# **Chapter Three**

- **3.1 Bioelectric Amplifiers**

- 3.2 Amplifier Circuit

- **3.3 Instrumentation Amplifier**

- **3.4 Filters**

- **3.5** Comparator

- 3.6 Active rectifier

- 3.7 Negative Impedance Converter and Gyrators

- 3.8 Data conversion unit (U3)

## **Chapter Three**

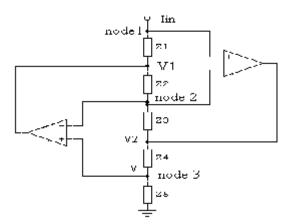

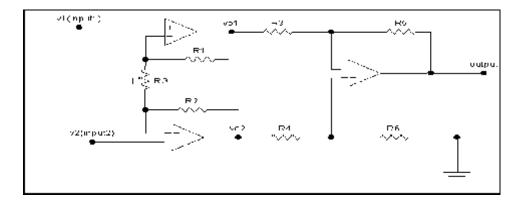

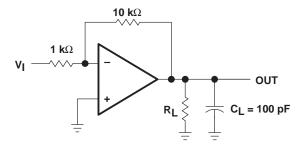

This chapter talk about operational amplifier unit (U3), OP AMP unit is shown in figure(3.1) which consisted of four OP AMP and 16 resistors with 2 potentiometers 3 diodes 3 capacitors each one separately from others . U2 introduces basics operational amplifier characteristics and applications including :instrumentation amplifier ,instrumentation rectifier ,Schmitt trigger comparator ,first and second low pass filter also high pass filter ,negative impedance converter .Then we will talk about data conversion unit U3. which contain D/A converter and A/D converter .

Figure (3.1): operational amplifier unit U2

#### **3.1 Bioelectric Amplifiers:**

Amplifiers used to process biopotentials are called bioelectric amplifiers, but this designation applies to a large number of different types of amplifier. The gain of a "bioelectric amplifier" for example, may be low, medium, or high (i.e., x10, x100, x1000, x10,000). Similarly, some bioelectric amplifiers are ac coupled, while others are dc coupled. The frequency response of "typical" bioelectric amplifiers may be from dc (or near dc. i.e.: 0.05 Hz) up to 100 kHz.

The high-frequency response is the frequency where the gain drops 3 dB below its midfrequency value. In some cases the -3 dB high-frequency point will be a frequency as low as 30 Hz, but in most cases it is usually 10 kHz. Specialized models used to process specific waveforms may have a particular response ECG amplifier, for example; usually have a frequency response of 0.05 to 100 Hz.

A few general-purpose amplifiers have adjustable frequency response and are thus usable for a wide range of applications. In general, it is wise to use only the minimum frequency response needed to insure good reproduction of the input waveform. This practice permits rejection of high-frequency noise.

Low-gain amplifiers are those with gain factors between x I and x 10. The unitygain (x1) amplifier is used mostly for isolation, buffering, and possibly impedance transformation between signal source and readout device. Low-gain amplifiers are often used for the measurement of action potentials and other relatively highamplitude bioelectric events. Medium-gain amplifiers are those that provide gain factors between x 10 and x 1000 and are used for the recording of ECG waveforms, muscle potentials, and so forth.

High-gain or low-level signal amplifiers have gain factors over x 1000. with some having factors as high as x 1.000,000. This type of amplifier is used in very sensitive measurements such as the recording of brain potentials (EEG).

Two important parameters in bioelectric amplifiers, especially those in the highand medium-gain classes, are *noise* and drift. Drift is the (spurious) change in output signal voltage due to changes in operating temperature (rather than input signal changes). Noise, in this case, normally is the thermal noise generated in resistances and semiconductor devices. Good design and prudent component selection reduce these problems to the negligible level in modern equipment.

All three classes of bioelectric amplifiers must have a very high input impedance. This requirement is the one commonality between all bioelectric amplifiers, because almost all bioelectric signal sources exhibit a high source impedance. Most bioelectric sources have an impedance between  $10^3$  and  $10^7 \Omega$ , and ordinary engineering design practices dictate an amplifier input impedance that is at least an order of magnitude higher than the source impedance. Modern amplifier (op-amp) devices have input impedances on the order of 1 tcraohm ( $10^{12}\Omega$ ).

### **3.2 Amplifier Circuit:**

Before jumping into op-amps, let's first go over some amplifier fundamentals. An amplifier has an input port and an output port. a port consists of two terminals, one of which is usually connected to the ground node. In a linear amplifier, the output signal = A ' input signal, where A is the amplification factor or "gain." Depending on the nature of the input and output signals, we can have amplifier gain: voltage gain (voltage out / voltage in). The circuit model of an amplifier is shown in Figure(3.2). The input port plays a passive role, producing no voltage of its own, and is modeled by a resistive element Ri called the input resistance. The output port is modeled by a dependent voltage source AVi in series with the output resistance Ro, where Vi is the potential difference between the input port terminals. Figure(3.2) shows a complete amplifier circuit, which consists of an input voltage source Vs in series with the source resistance Rs, and an output "load" resistance RL. From this figure, it can be seen that we have voltage-divider circuits at both the input port and the output port of the amplifier. This requires us to re-calculate Vi and Vo whenever a different source and load is used:

$$Vt = \left(\frac{Rt}{Rs + Rt}\right) Vs \dots 3.1$$

$$Vo = \left(\frac{Rl}{Ro + Rl}\right) AVs.....3.2$$

Figure (3.2): Circuit model of an amplifier circuit.

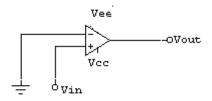

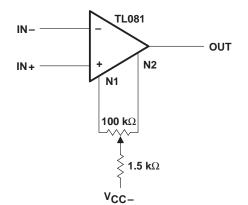

# 3.2.1 The Operational Amplifier: Ideal Op-Amp Model

The amplifier model shown in Figure (3.3) is redrawn in Figure (3.4) showing the standard op-amp notation. An op-amp is a "differential to single-ended" amplifier, i.e. it amplifies the voltage difference Vp - Vn = Vi at the input port and produces a voltage Vo at the output port that is referenced to the ground node of the circuit in which the op-amp is used.

Figure (3.3) : Standard op-amp

Figure (3.4): Ideal op-amp

The ideal model makes three simplifying assumptions or characteristics:

Gain is infinite:  $A = \infty$

Input resistance is infinite:  $Ri = \infty$

Output resistance is zero: Ro = 0

Applying these assumptions to the standard op-amp model results in the ideal opamp model shown in Figure (3.4). Because  $Ri = \infty$  and the voltage difference Vp - Vn = Vi at the input port is finite, the input currents are zero for an ideal op-amp:

in = ip = 0

Hence there is no loading effect at the input port of an ideal op-amp:

Vt=Vs

In addition, because Ro = 0, there is no loading effect at the output port of an ideal op-mp:

Finally, because  $A = \infty$  and Vo must be finite, Vi = Vp - Vn = 0, or

Vp = Vn

# 3.2.20pen loop gain:

$A_{oL}$  is the ratio of a change of output voltage to the change input voltage which is applied directly to the amplifier input terminals(not dependent on the circuits ).at ideal voltage amplifier we will get infinite open loop gain then:

$a \rightarrow \infty$

and ideal characteristics:

$$r_d = \infty$$

$$r_o = 0$$

$$i_p = i_n = 0$$

so A dependant on a .

# 3.2.3 Closed loop gain:

$A_{CL}$  In closed loop gain we refer to as ideal so:

Let  $a \rightarrow \infty$

Then:

$A_{ideal} = \lim_{a \to \infty} A \dots 3.4$

so the gain here independent of a and determine by the external resistance ratio.

### **3.2.4COMMON MODE REJICTION RATIO:**

The common mode rejection ratio (CMMR) is defined as the differential voltage gain divided by common mode voltage gain :

Figure(3.5): frequency response

Some care must be exercised in designing a circuit ,the higher CMMR the better ,A higher CMMR means that amplifying the wanted signal and discriminate against the common mode signal, data sheet usually specify CMMR in decibels :

$CMMR_{dB} = 20 \log CMMR.....3.6$

### 3.2.5 Bias And Offsets :

A diff amp has input bias and offsets that produce an output error when there is no input signal in many applications. When this false signal is amplified unwanted dc voltage  $V_{error}$  appear across the out put.

In many cause  $V_{error}$  can be ignored .such as in ac amplifier not important but at some kind precision dc amp needs to be taken into account .

Then by using nulling circuit we eliminate the bias current by using equal base resistors

Also to eliminate the effect of an input offset current and voltage using potentiometer by adjust this potentiometer with no input signal ,we can null or zero the output voltage.

### **3.2.6 Frequency Response:**

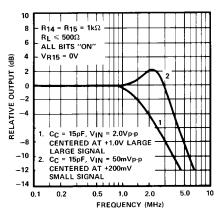

The frequency response of an amplifier is the graph of its gain versus the frequency. The gain expressed in dB is  $20 \log 10|G|$ . The frequency response of an op-amp is a low pass characteristic (*i.e.* passing low-frequency signals, attenuating high-frequency signals) as shown in Figure(3.6):

Figure(3.6) : Frequency response of op-amp.

The unity- gain frequency is the frequency at which the voltage gain equal 1. data sheet .Usually specify the value of  $f_{unity}$  because it represent the upper limit on the useful gain of an amp. The bandwidth is the frequency at which the power of the output signal is reduced to half that of the maximum output power. This occurs when the gain drops by 3 dB. In Figure (3.6), the bandwidth is B Hz. For all op-amps, the Gain\*Bandwidth product is a constant. Hence, if the gain of an op-amp is decreased, its operational bandwidth increases proportionally. This is an important trade-off consideration in op-amp circuit design. , we assumed that the op amp has infinite bandwidth.

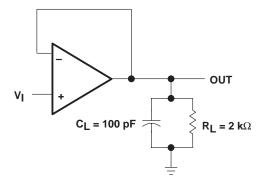

## 3.2.7 Slew rate :

The initial slop of the exponential wave form by compensating inside a capacitor is called slew rate :

this refer to the fastest response that op amp can have the data sheet of op amp always specifies the slew rate because this quantity limits the average signal response of an op amp, if the out put sine wave is very small or the frequency is very low, slew rate will distort the out put signal :

$S_s = 2\Pi f V_P \dots 3.8.1$

$S_s$ : initial slope of sine wave

f: frequency

$V_{P}$ : peak value

To avoid slew rate distortion of sine wave,  $S_s$  has to be less than or equal to  $S_R$  when the two are equal we are at the limit on the average of slew rate distortion at this :

$S_R = S_s = 2\Pi f V_P \dots 3.8.2$

Solving fore f:

$$f_{\max} = \frac{S_R}{2\Pi V_P} \dots 3.9$$

where  $f_{max}$  or (band width-large signal bandwidth of op amp) is the highest frequency that can amplified without slew rate distortion.

## **3.3 Instrumentation Amplifier**

Instrumentation amplifier, which is a differential voltage gain device that amplifies the difference between the voltages existing at its two input terminals, the main purpose of an instrumentation amplifier is to amplify a small signals riding on large common voltage.

The characteristics of instrumentation amplifier:

High input impedance.

High common mode rejection ratio.

Low output offset.

Low output impedance.

A basic instrumentation amplifier is made up of three operational amplifiers, and resistors. The voltage gain is set with external resistor (RG). The voltage gain is given by

$A_V = \frac{V_{OUT}}{Vin}$

Figure(3.7): Instrumentation Amplifier

## Derive of gain equitation:

Assume

$$A_3$$

unity gain ( $R_3 = R_4 = R_5 = R_6$ )

Assume  $R_1 = R_2$

$$V_{O2} - V_{O1} = (V_2 - V_1) \left( \frac{R_2}{R_G} + 1 + \frac{R_2}{R_G} \right) \dots 3.14$$

$$V_{O2} - V_{O1} = \left(V_2 - V_1\right) \left(\frac{2R_2}{R_g} + 1\right) \dots 3.15$$

$$A_{\nu} = \frac{2R_1}{R_g} + 1 \dots 3.16$$

then if  $A_3$  non zero

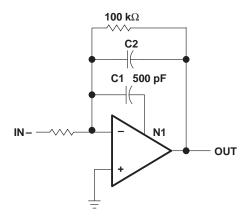

## **3.4 Filters:**

There are many types of medical instruments in which it is necessary to select the frequency components of the input signal because the signal generated with range of frequencies. It is often necessary to use filter to select the signals with wanted frequencies and reject the signal unwanted frequencies, in electroencephalograph (EEG-measure the electrical activity of brain), various brain states, and produce distinctive frequency band frequency band 4-8Hz indicate sleep,13-22Hz indicate a high state of alertness.

Filters may be used to direct these frequency bands to different channels to facilitate signal processing and disease diagnosis. filtering is useful in reducing noise.

## **\*** Active filter :

A filter can be either passive or active filter; passive filters are built with resistors, capacitors, and indicators. Active filters are built with resistors, capacitors, and op amps.

filter are usually categorized in manner which the output voltages varies with frequance of input voltage.

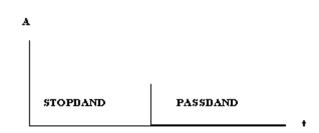

## 3.4.A passband and stopband attenuation :

it is the loss of signal with constant input voltage :

$Attenuation = \frac{V_{out}}{V_{out(mid)}} \qquad .....3.18$

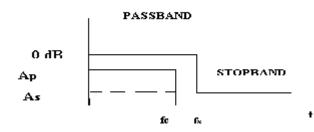

then the passband is set frequency between 0 and  $f_c$  (cutoff frequency).the stopband is all the frequency above  $f_s$ . The transition region is between  $f_c$  and  $f_s$  (stopband frequency). see figure (3.8) :

ATTENHATION

the five approximation trade off the characteristics of passband ,stopband .transition region .

## 3.4.B filter Approximate response :

each type of filter can be designed using five approximation used as compromise for ideal response to dealing with practical circuits . the approximation chosen by what acceptable application.

#### **3.4.B.1 Butterworth Approximation**:

The passband attenuation is zero through most of the passband and decrease gradually to  $A_p$  (gain passband) at edge of bass band, above edge the frequency the response rate roll off

roll off= 20n dB/decade ......3.19

n: order of the filter

the flat response is in passband.

The advantage of Butterworth is the flatness of the passand ,the major disadvantage is the relatively slow rate compared with other approximation.

## **3.4.B.2** Chebysheyev Approximation:

In some application a flat response is not important such as chebysheyev this preferred because it roll off faster in transition region than Butterworth filter. because of this the attenuation with a chebysheyev filter is always greater than the attenuation of the Butterworth .

# Ripple= $\frac{n}{2}$  ......3.20

## 3.4.B.3 Inverse Chebyshev Approximation

it has a flat passband response and rippled stopband response. the roll off rate in the transition region is comparable to roll off rate a chebyshev filter.

## **3.4.B.4 Elaiptic Approximation:**

if we need fastest possible roll off in the transition region if rippled stopband and the ripple passband is acceptable . this give us optimized transition region.

## 3.4.B.5 Bessel Approximation:

The Bessel approximation has a flat passband a monotonic stopband similar to those of the Butterworth approximation .however the roll off in the transition region is much less with a Bessel filter than with a Butterworth.

The Bessel approximation is producing a linear phase shift increase with frequency.

### 3.4.1 Low pass filter :

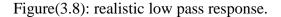

Figure(3.9): ideal low pass response

The low pass filter has the output frequency response ,the frequency of input signal voltage increase ,the output voltage decreases slightly .

when the input frequency reaches the upper critical (or break )frequency ( $f_c$ ), the output voltage has decreased to 70.7 % of the maximum output voltage. Which pass

all frequencies from zero to the cut off frequency and block all frequencies above cut off frequency.

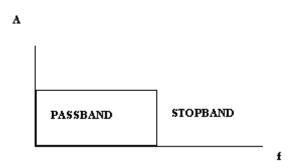

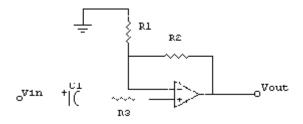

## 3.4.1.1 first order Low-pass filter:

First order noninverting low pass active filter, it has RC lag Figure(3.10):

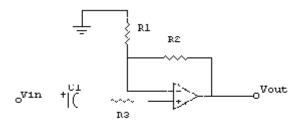

figure(3.10) first order low pass stage

$$V_O = \left(1 + \frac{R_2}{R_1}\right) V_C \quad \dots \quad 3.21$$

But:

$$\mathbf{K} = \left(1 + \frac{R_2}{R_1}\right) \dots 3.22$$

Multiple Vc:

$$V_c \times \frac{1}{j 2 \Pi f_c}$$

Then:

$$V_C = \frac{1}{1 + j2\Pi f R_i C} \text{ Vin } \dots 3.24$$

substitute eqauation 2.2 in 1:

$$\frac{V_o}{V_i} = k \left( \frac{1}{1 + j2\Pi f R_i} \right)$$

$$\left|\frac{V_o}{Vi}\right| = \frac{k}{\sqrt{1 + \left(j2\Pi f R_i\right)^2}} \dots 3.25$$

the cut off frequency at critical is given by:

$$\left|\frac{V_o}{Vi}\right| = \frac{1}{\sqrt{2}} \dots 3.26$$

$2\Pi f_C R_i C = 1$

$$\left|\frac{V_o}{V_i}\right| = \frac{k}{\sqrt{1 + \left(\frac{f}{f_c}\right)^2}} \dots 3.28$$

## 3.4.1.2 low pass filter second order:

second order or 2-pole stages Sallen-key, it consisted from two capacitor and two resistor, second order has a resonant frequency and a Q to determine how much peaking occurs, the roll off will be -40dB/decade.

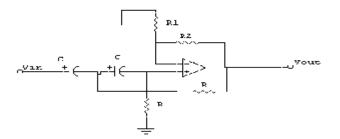

Figure (3.11): second order low pass filter

With kirchhoffs current low at node one:

or

by divider rule:

$$V_{1} = \frac{\frac{1}{SC_{3}}}{R_{3} + \frac{1}{SC_{3}}} V_{A} \dots 3.31$$

since

$$R_i = \infty, I_B \cong 0A$$

$$= \frac{V_A}{R_3 C_3 S + 1}$$

$$V_A = (R_3 C_3 S + 1)V_1 \dots 3.32$$

substituting equation \* in equation \*\* :

$$V_{1} = \frac{(R_{3})(V_{in}) + (R_{3}R_{2}C_{2}S)V_{o}}{(R_{3}C_{3}S + 1)(R_{2} + R_{3} + R_{3}R_{2}C_{2}S) - R_{2}} \dots 3.33$$

however:

therefore ;

$$V_{O} = \frac{A_{F}[(R_{3})(V_{in}) + (R_{3}R_{2}C_{2}S)(V_{O})]}{(R_{3}C_{3}S + 1)(R_{2} + R_{3} + R_{3}R_{2}C_{2}S) - R_{2}} \dots 3.36$$

solving the equation for  $\frac{V_O}{V_{in}}$ :

for the frequency above fp the gain of second – order low pass filter rolls off at rate of -40 dB/decade. with two real and equal roots this mean:

or

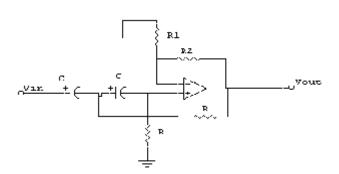

## 3.4.2 High pass filter:

Figure (3.12): ideal high-pass response.

The high pass filter has the output frequency response ,the frequency of input signal voltage increase ,the output voltage increase slightly .

when the input frequency reaches the above critical (or break )frequency ( $f_c$ ), the output voltage has increase to 70.7 % of the maximum output voltage. Which pass all frequencies above the cut off frequency and block all frequencies below cut off frequency.

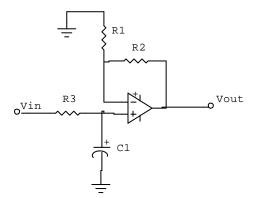

## 3.4.2.1 High pass filter first order:

First order noninverting highpass active filter the voltage gain: Figure (3.13):

figure(3.13): first order high pass stages .

the 3 dB frequency is given by :

3.4.2.2 high pass filter second order:

Figure(3.14): Second order high pass filter

$f_b$  : pole frequency

with second order low pass filter:

at

$$R_2 = R_1 \& C_1 = C2$$

then

$$Av = \frac{R_2}{R_1} + 1 \qquad .....3.42$$

$$Q = \frac{1}{3 - A_v} \qquad .....3.43$$

$$f_p = \frac{1}{2\Pi RC} \qquad .....3.44$$

## 3.5 Comparator:

Often we want to compare one voltage with other to see which is larger. Comparator is similar to an op amp because it has to input voltage (noninverting and inverting) and one out put voltage.

Then the pacemaker from the most application area the comparator play one of the most important roll to provide electronic digital pulse to determine the energy delivered to the heart.

## **Ideal comparator:**

To build comparator is to connect an op amp that has an open loop gain (A<sub>*OL*</sub>) that is finite ( $\infty$ ) see figure(3.15):

figure(3.15): ideal comparator

The minimum input voltage that produce saturation is :

if the input voltage more  $\pm V_{in}_{(min)}$  the output voltage will go to more positive or negative saturation.

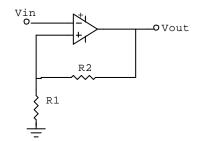

## **SCHMITT TRIGGER:**

if the input to comparator contains a large amount of noise, the out put will be effect with the noise, then by using a comparator with positive feed back this will prevent noise because produce two separate trip point. A comparator with positive feedback called a Schmitt trigger

Figure(3.16): Schmitt Trigger

When the comparator is positively saturated, a positive voltage is feedback to the noninverting input. This positive feed back voltage holds the out put in the high state. if the output negatively saturated a negative fed back to noninverting input, holding the output in the low state .the feed back fraction:

When the output is positively saturated, the reference voltage applied to the noninverting input is:

$V_{ref} = +BV_{sat}$  ......3.47

When the output is negatively saturated, the reference voltage is:

The output voltage will remain in a given state until the input voltage exceeds the voltage for that state.

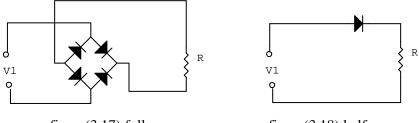

## 3.6 Active rectifier:

Semiconductor diodes that are connected in the half and full wave rectifier circuits in will have the output waveforms for sinusoidal inputs.

figure(3.17):full wave

These waveforms cause operation of the diode in the normal operating region for most of the input cycle.

The input voltage for rectifier is usually much larger than 0.7 volts, therefore there are no problems.

In some medical applications there are problems in some times exist to rectify very small AC voltages in millivolt such as the ECG signal, if the input voltage is less than 0.7 volts, which is the barrier voltage of silicon diodes, the diode is not operating in the normal range. For these low voltages, the diode is not turned on even though the diode is biased forward, this problem can be overcome by placing the diode within the feedback loop of an op amp.

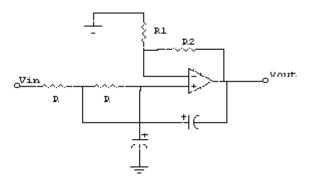

## **3.6 Instrument Rectifier**

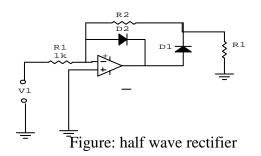

Half wave rectifier When the input signal goes positive output goes positive and turns on the diode. and the positive half cycle appears across the load resistor. input goes negative, the op-amp output goes negative and turns off the diode. Since the diode is open, no voltage appears across the load resistor. The final output is almost a perfect half-wave signal.

Figure(3.19): Half wave rectifier

There are two distinct *modes* or regions of operation. First, when the input voltage is positive, the diode is conducting and the operation is linear. In this case, the output voltage is fed back to the input, and we have negative feed. back. Second, when the input voltage is negative, the diode is nonconducting and the feedback path is open. In this case, the op-amp output is isolated from the load resistor.

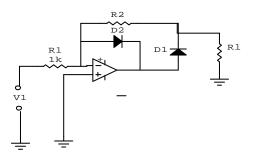

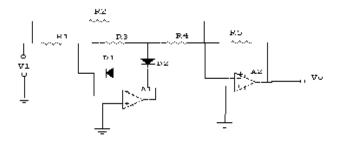

Full wave rectifier as the fig(3.21) we will a have a full wave out put .during the nonconducting half cycle of the diode  $D_2$ , the input positive voltage is applied to the output through resistors R22 this adds the order half cycle to the output to produce the full wave rectifier out put.

Figure(3.20):full wave rectifier

## 3.7 Negative Impedance Converter and Gyrators

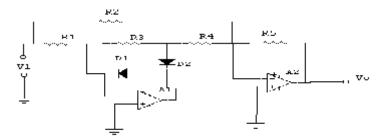

These two device can mimic properties of inductors while using only resistors and capacitors in additional to op amp.

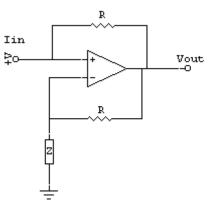

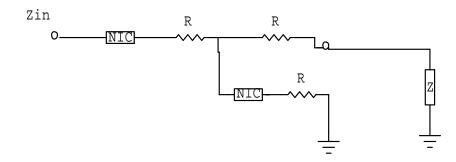

### 3.7.A NIC circuits:

The NIC they used op-amp ,resistors ,capacitors, it converts impedance to its

negative  $Z_{in}$  = -Z, the NIC there for converts a capacitor to a "back ward" inductor:

$$i_{in} = \frac{V_{in} - V_O}{R} \dots 3.49$$

substituting equation 1 in equation 2 :

then :

if Z capacitor then :

it mimics a backward inductor (inverse proportional with frequency)

## 3.7.B Gyrator:

whereas the gyrator converts an impedance to its inverse  $Z_{in} = \frac{R^2}{Z}$ . The gyrator coverts capacitor to true inductors :

Figure(3.22):gyrator

• Generalized impedance converter:

figure(3.23): Generalized impedance converter.

with node analysis:

from equation( 3.55):

substituting equation \* in equation (3.56) :

we sub . equation (3.58 )in equation (3.57):

$$\frac{\left(I\frac{Z_1Z_3}{Z}\right) + V - V}{Z_4} - \frac{V}{Z_5} = 0$$

$$\Rightarrow \quad \frac{IZ_1Z_3}{Z_2Z_4} = \frac{V}{Z_5} \Rightarrow \quad IZ_1Z_3Z_5 = VZ_2Z_4 \quad \dots \dots 3.60$$

since  $I = \frac{V}{Z_{in}} \Rightarrow \frac{V}{I} = Z_{in} \quad \dots \dots 3.61$

$$\therefore \frac{V}{I} = \frac{Z_{1}Z_{3}Z_{5}}{Z_{2}Z_{4}} \dots 3.62$$

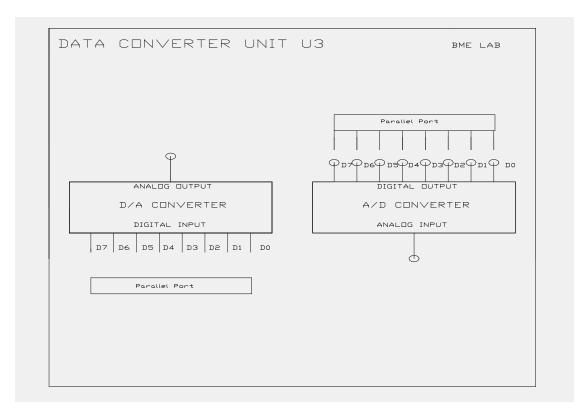

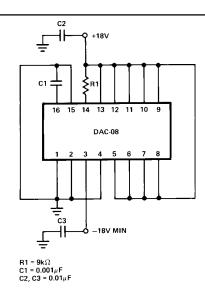

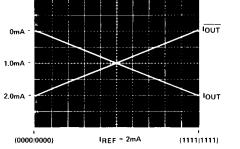

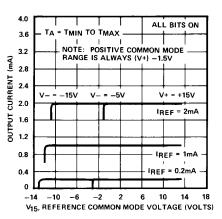

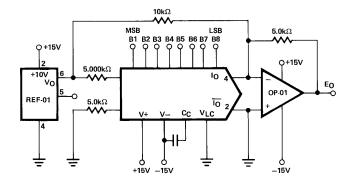

## 3.8 Data conversion unit (U3):

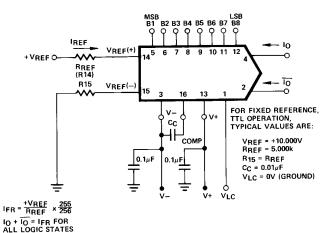

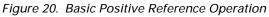

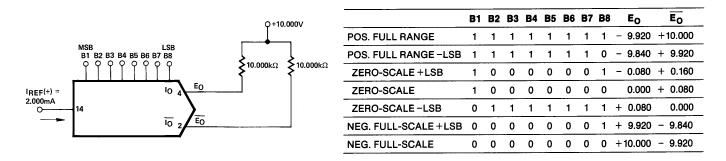

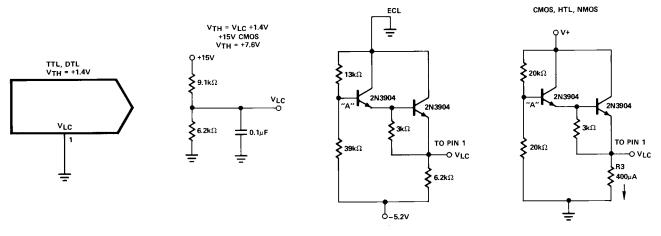

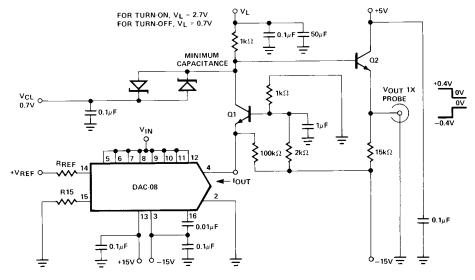

This unit data conversion is divided into A/D converter and D/A converter section .A/D converter one input analog convert 8 bit output digital (LEDs) female parallel port. D/A converter 8bit input female parallel convert to analog valve shown as figure (3.25).

figure(3.24) : Data Conversion Unit

## • Signal converter:

The microcomputer is a logic device it processes digital signal that are binary and discontinuous. On the other hand ,the real–word physical quantity such as temperature and pressure are continuous .

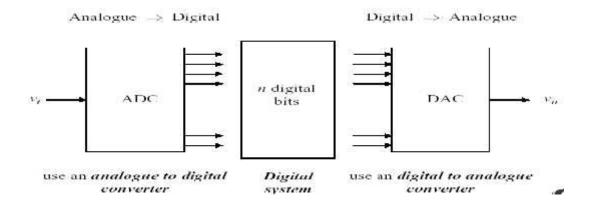

These are represented by equivalent electrical quantities called analog signal. Even through an analog signal may represent a real physical parameter with accuracy, it is difficult to process or store the analog signal for later use without introducing considerable error. Therefore, in microprocessor based industrial products, it is necessary to translate an analog signal into a digital signal. The electronic circuit that translates an analog signal into a digital signal is called an analog to digital (A/Dc) converter (A/Dc).

Similarly a digital signal needs to be translated into analog signal to represent a physical quantity .this translator is called a digital to analog (D/A) converter. Both A/D and D/A are also known as data conversion.

figure(3.25): ADc toDAc process

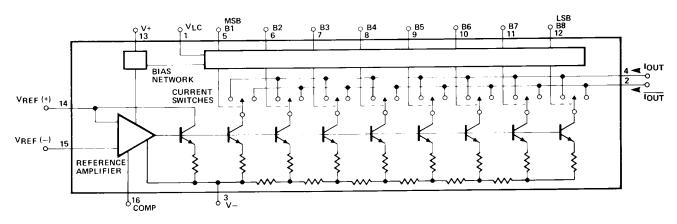

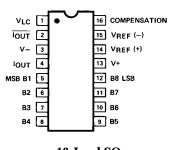

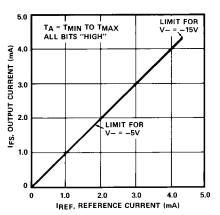

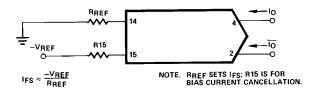

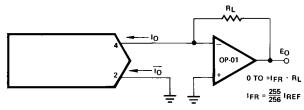

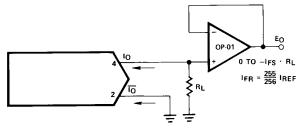

### **3.8.1 Digital to analog converter (D\ Ac):**

DAc are needed whenever the digitized signals through ADc are to be converted back to analog signal. Digital-to-Analog Converter – converts an digital signal (current-voltage) to digital value.

Most D/Ac uses a series of resistor in an R, 2R ,4R ,8R etc see the fig(1) each has double the previous resistor :

$$I_{O} = \frac{V_{REF}}{R} \left(\frac{A_{1}}{2} + \frac{A_{2}}{4} + \dots + \frac{A_{n}}{2^{n}}\right) \dots 3.63$$

figure (3.26)) : D/Ac summing amplifier with binary weighted input resistors.

## • D/Ac characteristics:

DAc has conversion speed as the successive approximation ADc.

## **3.8.2** Analog to digital signal A/Dc:

For the analog signals to be accepted by digital system or a microprocessor controller. The analog signals must be converted into digital signals. An A/Dc is used for:

1. Pc is a logic device (digital – discontinues).

2. The physical quantity as temperature, pressure is analog signal.

3. Digital signal reduction human error. Also it is easy to process or to store for later use.

(A\Dc) Analog-to-Digital Converter – converts an analog value to digital value (current-voltage).

### • A/Dc types:

- 1. Successive approximation

- 2. Flash

- 3. Ramp

- 4. Integrating

- 5. Tracking

- 6. Delta sigma converter

### • How do we represent our' analogue' signal as a digital code?

The number of signal levels depends upon the number of bits used e.g.:

4bit -  $2^4$  levels - 16 levels.

8bit-  $2^8$  levels - 256 levels.

16bit -  $2^{16}$  levels - 65536 levels.

## • A/DC basic conversion methods:

- 1. Direct conversion (voltage  $\Rightarrow$  binary).

- 1.1 Counting converter (includes DAC).

- 1.2 Successive approximation (includes DAC).

- 1.3 Flash

- Indirect conversion (voltage ⇒ time ⇒ binary)

Integrating ADC

- (single slope and dual slope)

# **Chapter four**

# Testing

- **\*** Unit testing:

- \* Sub-systems testing

- ✤ System testing .

## **Testing** :

The testing procedure is the most important part in the design of the hardware, to make sure that the hardware parts are working correctly and there are no errors.

The testing process includes the following stages:

- $\clubsuit$  unit testing.

- ✤ Sub-systems testing.

- ✤ System testing .

### Unit testing:

Here the testing is performed over the individual components are tested to ensure that they operate correctly.

All the electrical components, ICs are tested individually, were components noticed to function properly.

#### Sub-systems testing:

Here, the testing is performed over a collection of modules which have been integrated into sub-system.

The following sub-system were tested individually:

- 0804 A/Dc .

- 08cp D/Ac.

- Inverting amplifier.

- Noninverting amplifier .

- Instrumentation amplifier.

- Instrumentation rectifier.

- One poles and two poles low and high pass filter.

- Schmitt trigger.

- Negative impedance converter.

- Whetstone bridge .

## 0804 A/Dc testing:

Testing A/Dc 0804 is performed by choosing one input channel on specific voltage and display the digital value on the output ports.

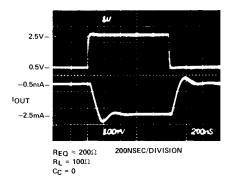

## **08cp D/Ac testing:**

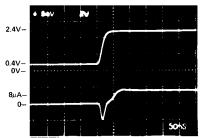

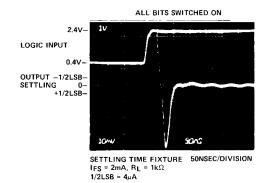

Testing D/Ac 08cp is performed by choosing 8-bit valve and observes the output Voltages.

## **Inverting amplifier:**

In testing this circuits ,we input voltage and observes the voltages output is inverted and the amplification of the input voltages according to calculation of the output voltages.

### Non inverting amplifier:

In testing this circuits ,we input voltage and observes the amplification of the output voltages according to calculation of the output voltages .

### Instrumentation amplifier:

.

In testing this circuits ,we input voltage and observes if amplified according to calculation of the output voltages .

### **Instrumentation rectifier:**

to make sure that is working correctly we input sinusoidal voltage and observes half wave output to halfwave circuit rectifier and the fullwave to fullwave circuit rectifier.

### One pole and two poles low and high pass filter:

Low pass filter we sure, if the input signal had frequency more than  $f_c$  Hz it was rejected, and if the input signal had a frequency less than  $f_c$  it was passed.

high pass filter we sure if the input signal had frequency less than  $f_c$  Hz it was rejected, and if the input signal had a frequency more than  $f_c$  it was passed.

#### Schmitt trigger:

In testing this circuit, we make sure that it worked correctly by comparing the input voltage with the reference voltage and making sure that the output is correct.

### Whetstone Bridge:

Connect whetstone bridge with sensor turn on the power supply adjust the potentiometer to zero output voltage then stimulates the sensor see the change in voltage output of the bridge.

### Negative impedance converter:

In testing this circuits, we observes the relation between the  $Z_{in}$  and the  $Z_{out}$ , when  $Z_{out}$  become  $-Z_{in}$ .

#### System testing:

After finishing the testing of sub-systems, the sub-systems are integrated to makeup a system . testing here is concerned with errors that generated from anticipated interaction between sub-system and system components .

The system testing itself is divided into the following stages:

- 1. Sensor unit test .

- 2. Operation amplifier unit test.

- 3. Data conversion unit test.

At first stage, sensor are connected to input resistance whetstone bridge, then stimulate sensor read output voltage of bridge.this testing was done.

Second stage, operation amplifier unit tested by connect input to of from output of sensor unit or function generator to oscilloscope and see the output. this testing is accomplished successfully.

Data conversion unit , take input voltage from sensor unit output or from operational amplifier unit first to input of A/Dc then to D/Ac .this testing was done successfully and achieved the desired results.

# **CHAPTER FIVE**

**Conclusion and Future work**

# **Conclusion and future work**

We have built the experimental board .And we have tested the board according to experiments sheet.

For future work we recommend to interface this board to the personal computer.

### **A. Book References:**

1. George Clayton &Bruce Newby, (1992), "<u>Operational Amplifiers</u>", (3<sup>rd</sup> ed.), Newnes

2. Albert Paul Malvino, (1999), "Electronic Principles", (6th ed.), Mc Graw-hill.

3. W.Bolten, (1996), "sensors and transducer" (3<sup>rd</sup> ed.).

4. Johan G.Webester, (1988), "medical Instromentaion" (3<sup>rd</sup> ed.), National Academy.

5. Johan J .Carr&Johan M.brown, (1993),"<u>Introduction to Biomedical Equipment</u>", (2<sup>nd</sup> ed.), Prentice Hall.

### **B. Internet Reference:**

6. http://www.electronic.com/search,op+amp

# **PREFACE:**

This manual is designed to help the user with the, insight of biomedical Electronics. It discusses implementation of various IC s for industrial utilities. By the end of the course user are expected to have understanding of the electronic devices and their usage.

# **Bioelectronics Lab Manual**

### Laboratory

#### **Operational Amplifier**

### Name

### **PURPOSE:**

- 1. Investigate the non-inverting amplifier .calculate and measure the voltage gain .

- 2. Investigate the inverting amplifier. .calculate and measure the voltage gain.

- 3. Determine characteristics of the circuit

#### **EQUIPMENT:**

- 1. Operation amplifier U2.

- 2. Function generator.

- 3. Oscilloscope.

- 4. DVM.

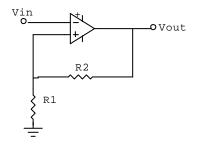

### A. Non-inverting Amplifier

#### 1. Preliminary design work

before you come to lab ,design and sketch a noninverting amplifier

### Build and test this circuit:

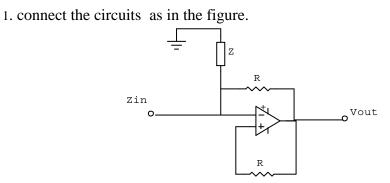

. 1. connect the circuits as the figure

2. Apply a small amplitude sine wave from signal generator, and verify the operation of this circuit..

3. Use a DMM to measure  $R_1$ ,  $R_2$  and calculate the gain.

$$R_1 = \Omega$$

$R_2 = \Omega$

$$gain=1+\frac{R_2}{R_1} \ .$$

4. mesure the input voltage and the output voltage, calculate the gain.

$$V_{in} = v$$

$V_{out} = v$

$$gain = \frac{V_{out}}{V_{in}}$$

### **B.** inverting Amplifier

### 1. Preliminary design work

before you come to lab ,design and sketch a inverting amplifier

### Build and test this circuit:

1. connect the circuits as the figurer

2. Apply a small amplitude sine wave from signal generator , and verify the operation of this circuit..

3. Use a DMM to measure  $R_1$ ,  $R_2$  and calculate the gain.

$$R_1 = \qquad \Omega \\ R_2 = \qquad \Omega$$

$$gain = -\frac{R_2}{R_1} = .$$

4. mesure the input voltage and the output voltage , calculate the gain .

$$V_{in} = v$$

$$V_{out} = v$$

$$gain = -\frac{V_{out}}{V_{in}} =$$

# **Bioelectronics Lab Manual**

### Laboratory

### SCHIMIT TRIGER

Name

# **PURPOSE:**

- 1. Sketch the comparator circuit that has positive feedback.

- 2. Obtain the output of the with square wave.

- 3. Determine characteristics of the circuit

### **EQUIPMENT:**

- 1. operation amplifier U2.

- 2. Function generator.

- 3.oscilloscope.

4.DVM.

### **Build and test this circuit:**

1. connect the circuits as the figure.

**Figure: Schmitt trigger**

- 2. Connect the triangle wave voltage from signal generator.

- 3. Calculate the voltage feedback:

$$V_{fb} = \pm \frac{R_1}{R_1 + R_2} V_{sat}$$

4. Slowing increase input voltage and note the output.

# **Bioelectronics Lab Manual**

Laboratory

Instrumentation

### rectifier

### Name

### **PURPOSE:**

to understand operation of the circuits and determine characteristics of the circuits

### **EQUIPMENT:**

- 1. Operation amplifier U2.

- 2. Function generator.

- 3. Oscilloscope.

- 4. DVM.

### A. Half wave rectifier

### **Build and test this circuit:**

1. connect the circuits as in the figure.

- 2. connect sin wave voltage from signal generator

- 3. draw the output voltage

### A. full wave rectifier Build and test this circuit:

1. Connect the circuits as in the figure

Figure: full wave rectifier

- 2. Connect sin wave voltage from signal generator

- 3. Draw the output voltage

# **Bioelectronics Lab Manual**

### Laboratory

Instrumentation amplifier

Name

### **PURPOSE:**

1. determine the output of instrumentation amplifier

2.determine characteristics of the circuit

#### **EQUIPMENT:**

Operation amplifier U2.

Function generator.

Oscilloscope.

DVM.

### **Build and test this circuit:**

1. connect the circuits as in the figure

### Figure(3.6): Instrumentation Amplifier

- 2. connect input signal to V1,V2

- 3. measure  $R_1, R_3, R_5, R_G$

$$R_{1} =$$

$$R_{3} =$$

$$R_{5} =$$

$$R_{G} =$$

$$A_{V} = \left(\frac{2R_{1}}{R_{G}} + 1\right) \left(\frac{R_{5}}{R_{3}}\right) =$$

4. draw the out put voltage

# **Bioelectronics Lab Manual**

#### Laboratory

Negative Impedance Converter

Name

# **PURPOSE:**

1. To know principle of operation and characteristics of circuit .

2.To find output impedance.

### **EQUIPMENT:**

- 1. Operation amplifier U2.

- 2. Function generator.

- 3. Oscilloscope.

- 4. DVM.

### Build and test this circuit:

2. measure C , connect  $V_{in}$  and obsearve.

$$Z_{in} = -Z$$

$V_{in} =$

4. draw the output voltage

$$V_{out} =$$

### **Bioelectronics Lab Manual**

#### Laboratory

Filters

Name

#### **PURPOSE:**

- 1. Know principle of operation the circuits

- 2. Determine Characteristics of first and second order low pass filter.

- 3. Determine Characteristics of first and second order high pass filter.

- 4. Determine the frequency response of low and high pass filter.

#### **EQUIPMENT:**

- 1. Operation amplifier U2.

- 2. Function generator.

- 3. oscilloscope.

- 4. DVM.

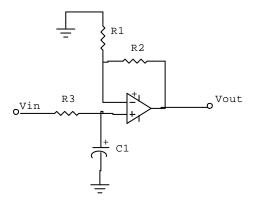

### A. low pass filter

### 1. First order

#### **Build and test this circuit:**

1. connect the circuits as in the figure

figure: first order low pass filter

- 2. Adjust the signal generator to sinusoidal waveform

- 3. Vary the frequency and observe  $V_{out}$

- 4. Calculate the voltage gain of the circuit

$$Av = \frac{R_2}{R_1} + 1 =$$

5. Sketch the frequency response the circuit

#### 2. Second order

### **Build and test this circuit:**

2. connect the circuits as in the figure

Figure: second order low pass filter

- 2. Adjust the signal generator to sinusoidal waveform

- 3. Vary the frequency and observe  $V_{out}$

- 4. Calculate the voltage gain of the circuit

$$Av = \frac{R_2}{R_1} + 1 =$$

5. Sketch the frequency response the circuit

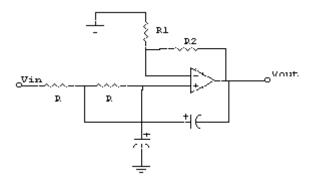

# **B. high pass filter:**

### 1.first order

### **Build and test this circuit:**

3. connect the circuits as in the figure

Figure: first order high pass filter

- 2. Adjust the signal generator to sinusoidal waveform

- 3. Vary the frequency and observe  $V_{out}$

- 4. Calculate the voltage gain of the circuit

$$Av = \frac{R_2}{R_1} + 1 =$$

5. Sketch the frequency response the circuit

### 2. second order

### **Build and test this circuit:**

4. connect the circuits as in the figure

Figure: Second order high pass filter

2. Adjust the signal generator to sinusoidal waveform

- 3. Vary the frequency and observe  $V_{out}$

- 4. Calculate the voltage gain of the circuit

$$Av = \frac{R_2}{R_1} + 1 =$$

5. Sketch the frequency response the circuit

**Bioelectronics Lab Manual**

Laboratory

**Data conversions**

Name

### **PURPOSE:**

To learn ADc and DAc technique of the temperature data using Wheatstone Bridge .

### **EQUIPMENT:**

- 1. Data conversion unit U2.

- 2. Temperature sensor.

- 3. DVM.

- 4. Sensor unit U1.

### **Build and test this circuit:**

1. Connect the temperature sensors to the sensor input terminals of the sensor unit.

2. Adjusting the potentiometer of the set the bridge to balance so the current indication is zero.

3. Connect between the bridge out put of and input of ADc and the DVM .

4. Increase the temperature of the sensors and measure the analog and digital output and fill the table with the results.

|   | Analog |    | Digital (8 bit) |    |    |    |    |    |    |  |  |

|---|--------|----|-----------------|----|----|----|----|----|----|--|--|

|   | volts  | D7 | D6              | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

| 1 |        |    |                 |    |    |    |    |    |    |  |  |

| 2 |  |  |  |  |  |

|---|--|--|--|--|--|

| 3 |  |  |  |  |  |

| 4 |  |  |  |  |  |

| 5 |  |  |  |  |  |

Table: ADc

5.repeat step 6 but connect ADc out put to DAc input and compare the values

|    |    |    | Digital | (8 bit) |    |    |    | Analog |   |

|----|----|----|---------|---------|----|----|----|--------|---|

| D7 | D6 | D5 | D4      | D3      | D2 | D1 | D0 | volts  |   |

|    |    |    |         |         |    |    |    |        | 1 |

|    |    |    |         |         |    |    |    |        | 2 |

|    |    |    |         |         |    |    |    |        | 3 |

|    |    |    |         |         |    |    |    |        | 4 |

|    |    |    |         |         |    |    |    |        | 5 |

Table :DAc

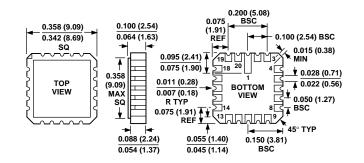

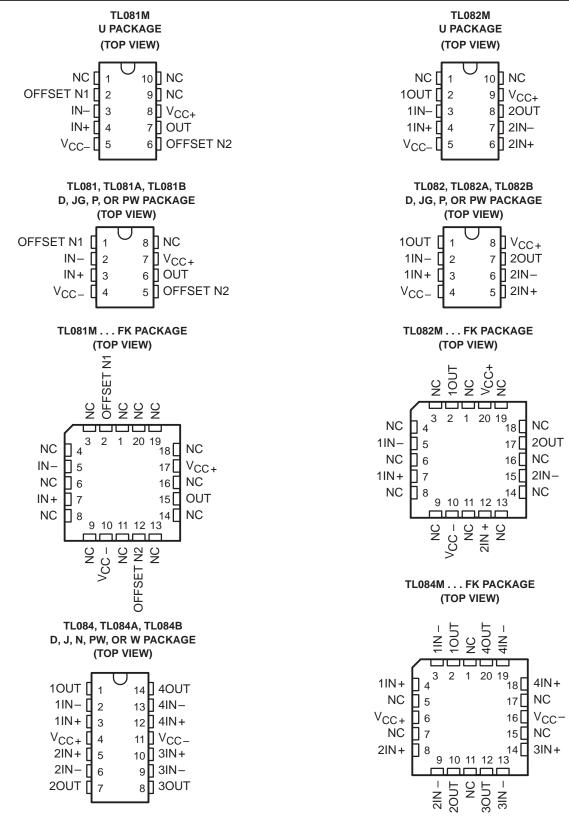

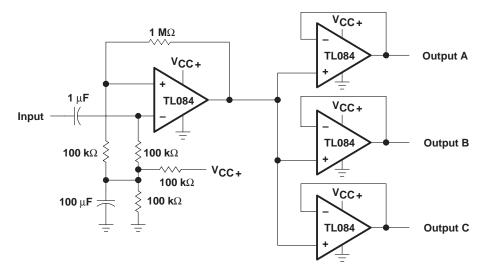

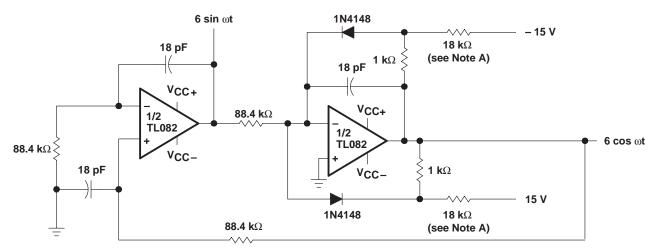

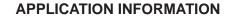

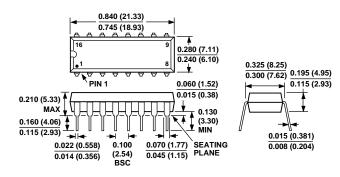

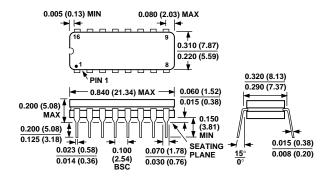

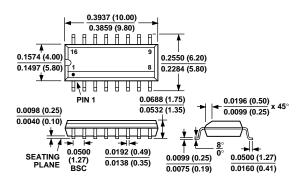

#### TL081, TL081A, TL081B, TL082, TL082A, TL082B TL082Y, TL084, TL084A, TL084B, TL084Y JFET-INPUT OPERATIONAL AMPLIFIERS SLOS081E – FEBRUARY 1977 – REVISED FEBRUARY 1999

- Low Power Consumption

- Wide Common-Mode and Differential Voltage Ranges

- Low Input Bias and Offset Currents

- Output Short-Circuit Protection

- Low Total Harmonic Distortion . . . 0.003% Typ

#### description

- High Input Impedance . . . JFET-Input Stage

- Latch-Up-Free Operation

- High Slew Rate ... 13 V/μs Typ

- Common-Mode Input Voltage Range Includes V<sub>CC+</sub>

The TL08x JFET-input operational amplifier family is designed to offer a wider selection than any previously developed operational amplifier family. Each of these JFET-input operational amplifiers incorporates well-matched, high-voltage JFET and bipolar transistors in a monolithic integrated circuit. The devices feature high slew rates, low input bias and offset currents, and low offset voltage temperature coefficient. Offset adjustment and external compensation options are available within the TL08x family.

The C-suffix devices are characterized for operation from  $0^{\circ}$ C to  $70^{\circ}$ C. The I-suffix devices are characterized for operation from  $-40^{\circ}$ C to  $85^{\circ}$ C. The Q-suffix devices are characterized for operation from  $-40^{\circ}$ C to  $125^{\circ}$ C. The M-suffix devices are characterized for operation over the full military temperature range of  $-55^{\circ}$ C to  $125^{\circ}$ C.

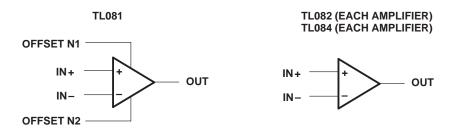

#### symbols

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1999, Texas Instruments Incorporated On products compliant to MIL-PRF-38535, all parameters are tested unless otherwise noted. On all other products, production processing does not necessarily include testing of all parameters.

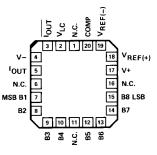

#### TL081, TL081A, TL081B, TL082, TL082A, TL082B TL082Y, TL084, TL084A, TL084B, TL084Y JFET-INPUT OPERATIONAL AMPLIFIERS SLOS081E – FEBRUARY 1977 – REVISED FEBRUARY 1999

NC – No internal connection

|                      |                                |                                 |                                 |                                  | AVA                   | PACKAGE                |                                 |                                 |               |                     |                     |                     |

|----------------------|--------------------------------|---------------------------------|---------------------------------|----------------------------------|-----------------------|------------------------|---------------------------------|---------------------------------|---------------|---------------------|---------------------|---------------------|

| т <sub>А</sub>       | V <sub>IO</sub> max<br>AT 25°C | SMALL<br>OUTLINE<br>(D008)      | SMALL<br>OUTLINE<br>(D014)      | CHIP<br>CARRIER<br>(FK)          | CERAMIC<br>DIP<br>(J) | CERAMIC<br>DIP<br>(JG) | PLASTIC<br>DIP<br>(N)           | PLASTIC<br>DIP<br>(P)           | TSSOP<br>(PW) | FLAT<br>PACK<br>(U) | FLAT<br>PACK<br>(W) | CHIP<br>FORM<br>(Y) |

|                      | 15 mV<br>6 mV<br>3 mV          | TL081CD<br>TL081ACD<br>TL081BCD | _                               | _                                | _                     | _                      | _                               | TL081CP<br>TL081ACP<br>TL081BCP | TL081CPW      | _                   | _                   | _                   |

| 0°C<br>to<br>70°C    | 15 mV<br>6 mV<br>3 mV          | TL082CD<br>TL082ACD<br>TL082BCD | _                               | _                                | _                     | _                      | _                               | TL082CP<br>TL082ACP<br>TL082BCP | TL082CPW      | _                   | _                   | TL082Y              |

|                      | 15 mV<br>6 mV<br>3 mV          | _                               | TL084CD<br>TL084ACD<br>TL084BCD | _                                | _                     | _                      | TL084CN<br>TL084ACN<br>TL084BCN | _                               | TL084CPW      | _                   | _                   | TL084Y              |

| −40°C<br>to<br>85°C  | 6 mV<br>6 mV<br>6 mV           | TL081ID<br>TL082ID<br>TL084ID   | TL084ID                         | _                                | _                     | _                      | TL084IN                         | TL081IP<br>TL082IP              | _             | _                   | _                   | _                   |

| −40°C<br>to<br>125°C | 9 mV                           | _                               | TL084QD                         | _                                | _                     | _                      | _                               | _                               | _             |                     | _                   | _                   |

| −55°C<br>to<br>125°C | 6 mV<br>6 mV<br>9 mV           | _                               | _                               | TL081MFK<br>TL082MFK<br>TL084MFK | TL084MJ               | TL081MJG<br>TL082MJG   | _                               | _                               | _             | TL081MU<br>TL082MU  | TL084MW             | _                   |

The D package is available taped and reeled. Add R suffix to the device type (e.g., TL081CDR).

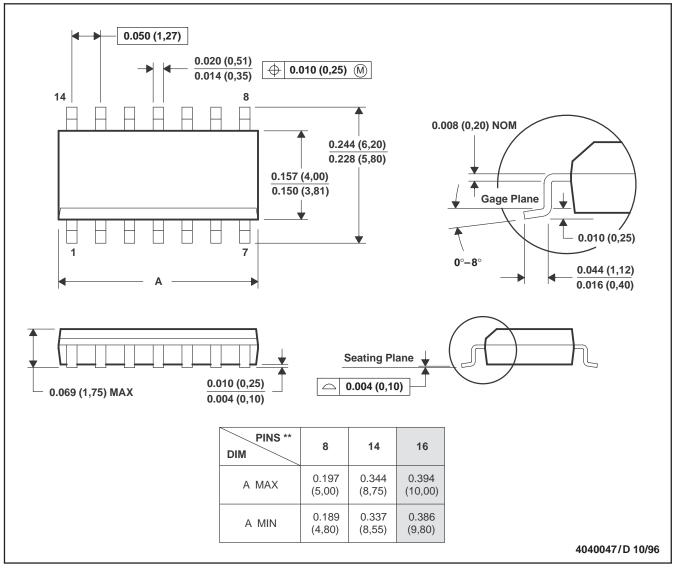

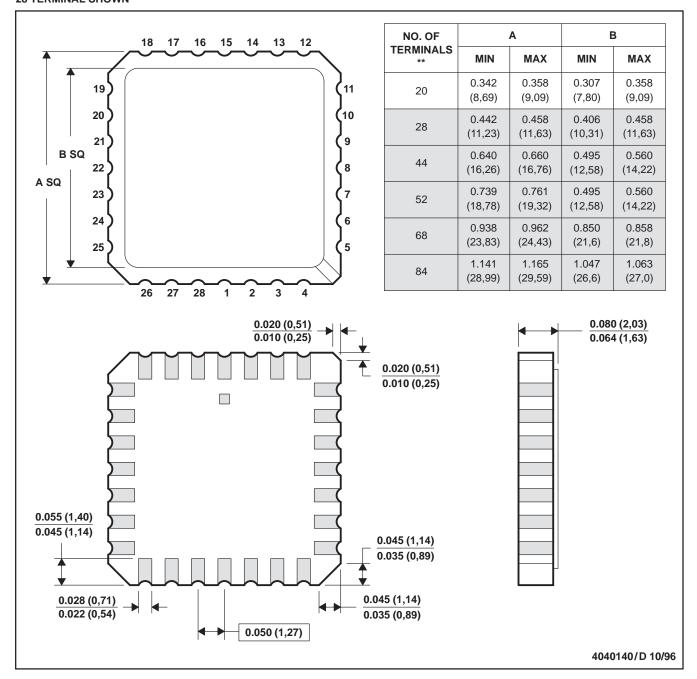

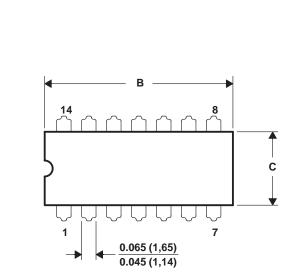

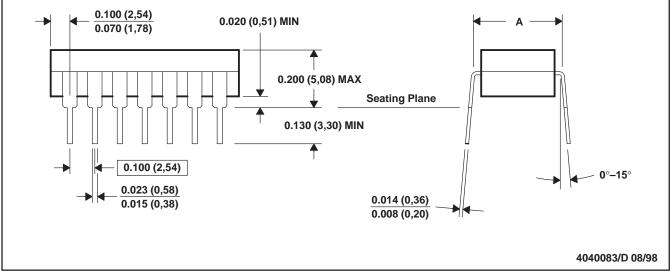

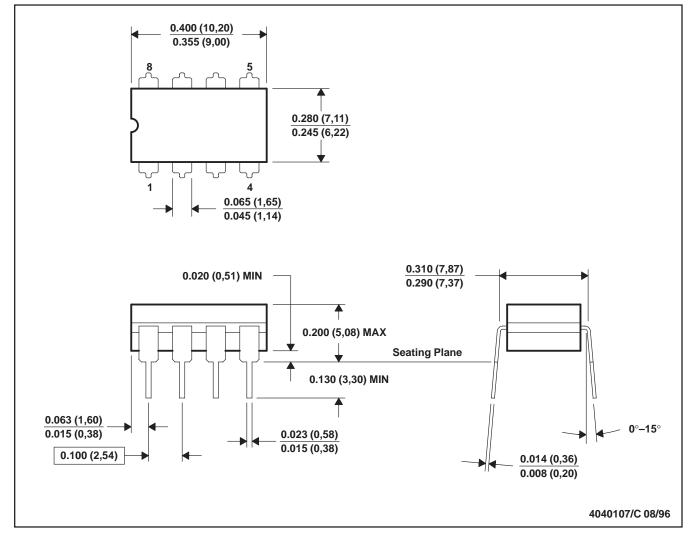

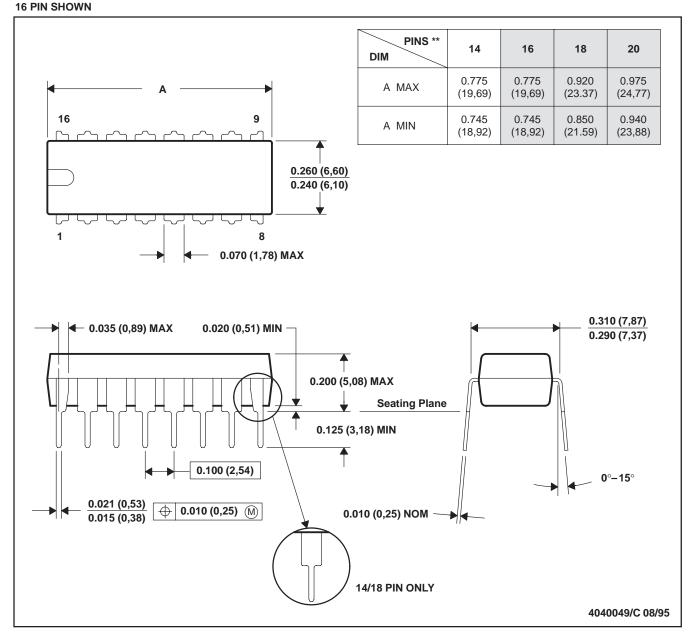

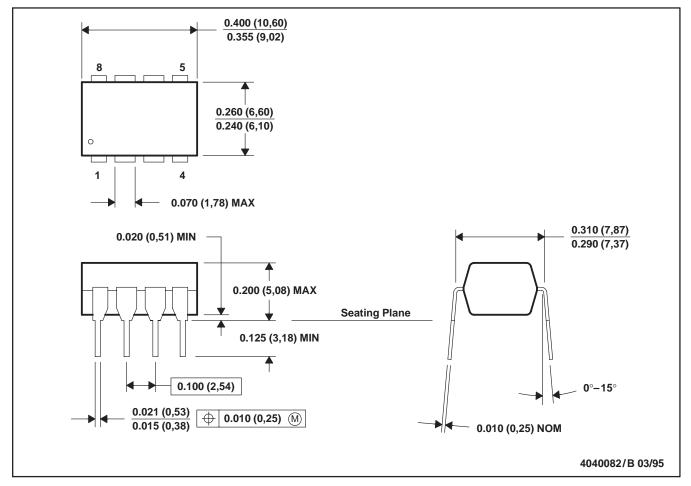

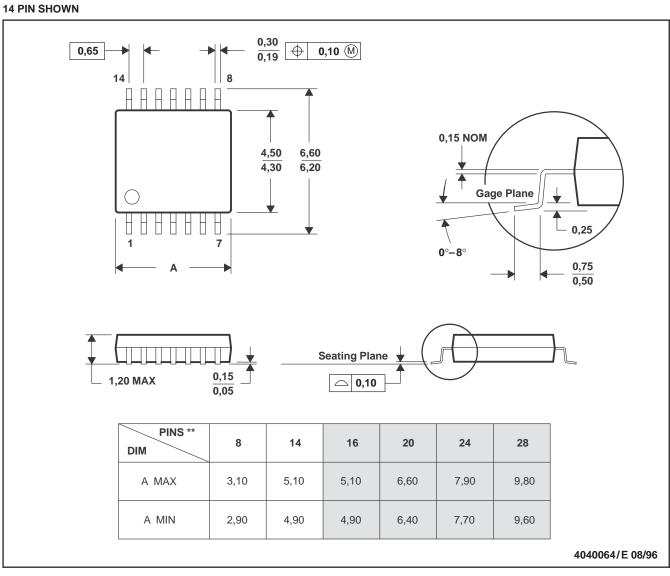

TL081, TL081A, TL081B, TL082, TL082A, TL082B TL082Y, TL084, TL084A, TL084B, TL084Y JFET-INPUT OPERATIONAL AMPLIFIERS SLOSOBIE - FEBRUARY 1977 - REVISED FEBRUARY 1999

TEXAS INSTRUMENTS POST OFFICE BOX 65533\* DALLAS, TEXAS 75265

#### TL081, TL081A, TL081B, TL082, TL082A, TL082B TL082Y, TL084, TL084A, TL084B, TL084Y JFET-INPUT OPERATIONAL AMPLIFIERS SLOS081E – FEBRUARY 1977 – REVISED FEBRUARY 1999

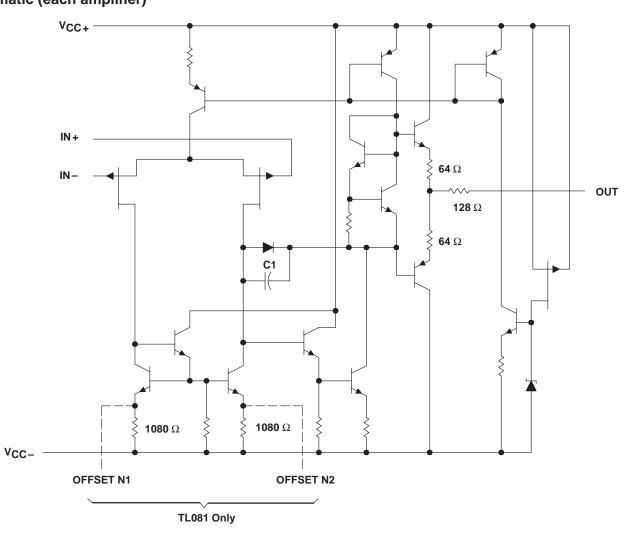

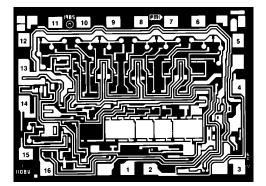

schematic (each amplifier)

Component values shown are nominal.

#### TL081, TL081A, TL081B, TL082, TL082A, TL082B TL082Y, TL084, TL084A, TL084B, TL084Y JFET-INPUT OPERATIONAL AMPLIFIERS SLOS081E - FEBRUARY 1997 - REVISED FEBRUARY 1999

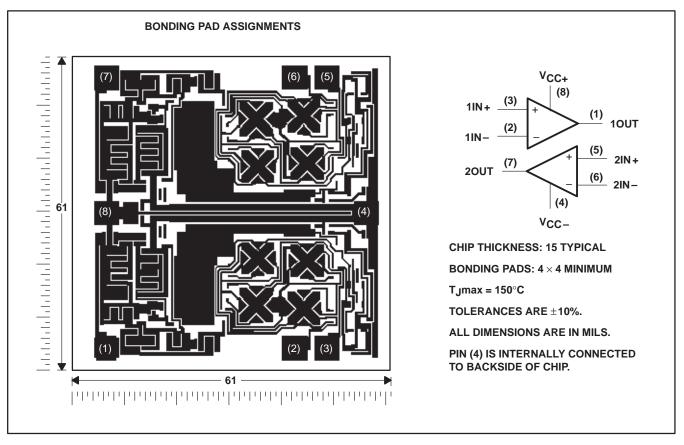

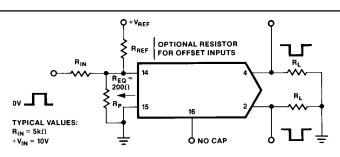

### **TL082Y chip information**

These chips, when properly assembled, display characteristics similar to the TL082. Thermal compression or ultrasonic bonding may be used on the doped-aluminum bonding pads. Chips may be mounted with conductive epoxy or a gold-silicon preform.

# TL081, TL081A, TL081B, TL082, TL082A, TL082B TL082Y, TL084, TL084A, TL084B, TL084Y JFET-INPUT OPERATIONAL AMPLIFIERS

SLOS081E - FEBRUARY 1977 - REVISED FEBRUARY 1999

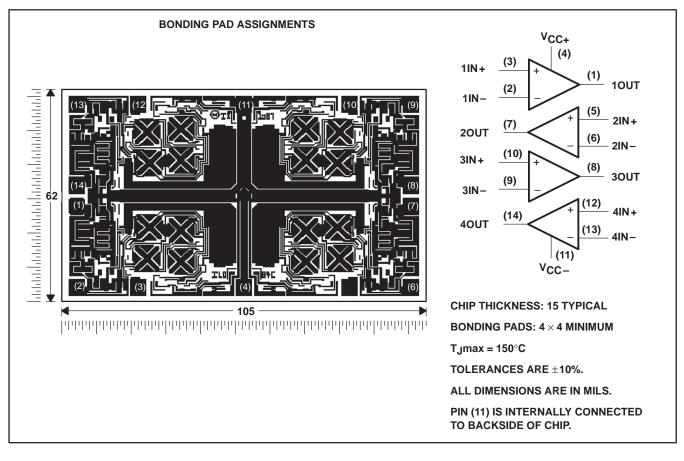

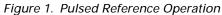

#### **TL084Y chip information**

These chips, when properly assembled, display characteristics similar to the TL084. Thermal compression or ultrasonic bonding may be used on the doped-aluminum bonding pads. Chips may be mounted with conductive epoxy or a gold-silicon preform.

# TL081, TL081A, TL081B, TL082, TL082A, TL082B TL082Y, TL084, TL084A, TL084B, TL084Y JFET-INPUT OPERATIONAL AMPLIFIERS

SLOS081E - FEBRUARY 1977 - REVISED FEBRUARY 1999

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

|                                                              |                           | TL08_C<br>TL08_AC<br>TL08_BC | TL08_I      | TL084Q      | TL08_M      | UNIT |  |  |

|--------------------------------------------------------------|---------------------------|------------------------------|-------------|-------------|-------------|------|--|--|

| Supply voltage, V <sub>CC+</sub> (see Note 1)                |                           | 18                           | 18          | 18          | 18          | V    |  |  |

| Supply voltage V <sub>CC</sub> – (see Note 1)                |                           | -18                          | -18         | -18         | -18         | V    |  |  |

| Differential input voltage, VID (see Note 2)                 |                           | ± 30                         | ± 30        | ± 30        | ± 30        | V    |  |  |

| Input voltage, VI (see Notes 1 and 3)                        |                           | ±15                          | ±15         | ±15         | ±15         | V    |  |  |

| Duration of output short circuit (see Note 4)                |                           | unlimited                    | unlimited   | unlimited   | unlimited   |      |  |  |

| Continuous total power dissipation                           |                           | See Dissipation Rating Table |             |             |             |      |  |  |

| Operating free-air temperature range, TA                     |                           | 0 to 70                      | – 40 to 85  | - 40 to 125 | – 55 to 125 | °C   |  |  |

| Storage temperature range, T <sub>Stg</sub>                  |                           | – 65 to 150                  | – 65 to 150 | – 65 to 150 | – 65 to 150 | °C   |  |  |

| Case temperature for 60 seconds, T <sub>C</sub>              | FK package                |                              |             |             | 260         | °C   |  |  |

| Lead temperature 1,6 mm (1/16 inch) from case for 60 seconds | J or JG package           |                              |             |             | 300         | °C   |  |  |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | D, N, P, or<br>PW package | 260                          | 260         | 260         |             | °C   |  |  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values, except differential voltages, are with respect to the midpoint between V<sub>CC+</sub> and V<sub>CC-</sub>.

2. Differential voltages are at IN+ with respect to IN-.

The magnitude of the input voltage must never exceed the magnitude of the supply voltage or 15 V, whichever is less. 3.

4. The output may be shorted to ground or to either supply. Temperature and/or supply voltages must be limited to ensure that the dissipation rating is not exceeded.

| PACKAGE     | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING<br>FACTOR | DERATE<br>ABOVE T <sub>A</sub> | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|-------------|---------------------------------------|--------------------|--------------------------------|---------------------------------------|---------------------------------------|----------------------------------------|

| D (8 pin)   | 680 mW                                | 5.8 mW/°C          | 32°C                           | 460 mW                                | 373 mW                                | N/A                                    |

| D (14 pin)  | 680 mW                                | 7.6 mW/°C          | 60°C                           | 604 mW                                | 490 mW                                | 186 mW                                 |

| FK          | 680 mW                                | 11.0 mW/°C         | 88°C                           | 680 mW                                | 680 mW                                | 273 mW                                 |

| J           | 680 mW                                | 11.0 mW/° C        | 88°C                           | 680 mW                                | 680 mW                                | 273 mW                                 |

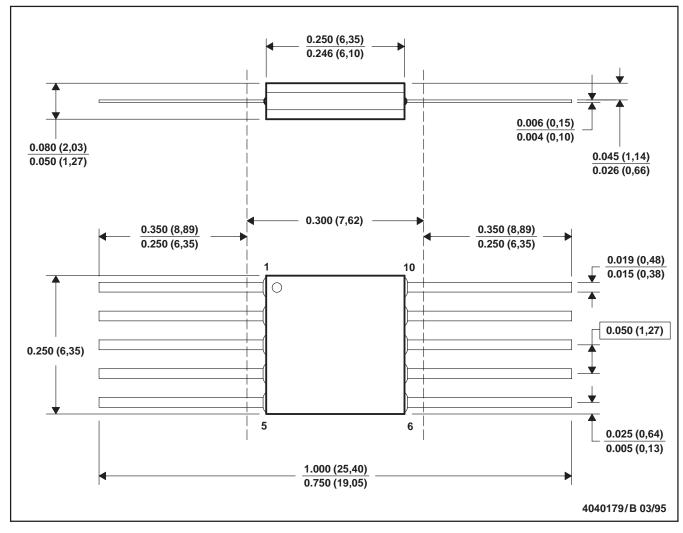

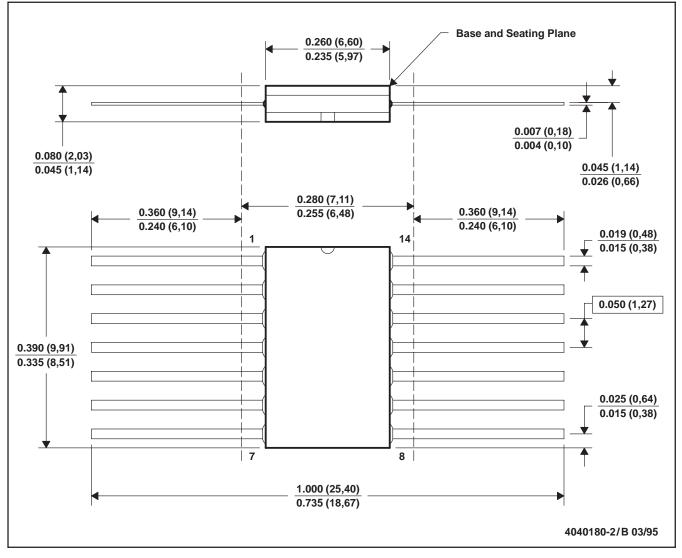

| JG          | 680 mW                                | 8.4 mW/°C          | 69°C                           | 672 mW                                | 546 mW                                | 210 mW                                 |