Palestine Polytechnic University Deanship of Graduate Studies and Scientific Research

Performance-Power Enhancement on High-Scale Heterogeneous Multi Processors (HMP) using Genetic Algorithms (GA)

> Submitted By: Ahmad N. M. Aljabari

Thesis submitted in partial fulfillment of requirements of the degree Master of Science in Informatics June, 2012 The undersigned hereby certify that they have read and recommend to the Deanship of Graduate Studies and Scientific Research at Palestine Polytechnic University the acceptance of a thesis entitled: Performance-Power Enhancement on High-Scale Heterogeneous Multi Processors (HMP) using Genetic Algorithms (GA) submitted by Ahmad N Aljabari, in partial fulfillment of the requirements for the degree of Master in Informatics.

Graduate Advisory Committee:

Committee Chair Name (Supervisor), University:

Dr. Mohammed Aldasht, Palestine Polytechnic University

Committee Member Name, University:

Dr. Hashem Tamimi, Palestine Polytechnic University Signature: Hallen Jam- Date: 3/2/2012

Committee Member Name, University:

Signature: Date: 412012

Approved for the Deanship:

Dean of Graduate Studies and Scientific Research - Palestine Polytechnic Uni-

Signature: Sahtral Date: 4.7-2012 Prof. Dr. Karim Tahbonh

نبيذة الأطروحية

عملية المقايضة بين مقدار الطاقة المستنفذة وجودة الأداء تعتبر من القضايا المهمة والحرجة في أنظمة المعالجة والتي تضم عدة كبير من المعالجات الغير متجانسة. و خصوصا في الأنظمة الحديثة والمتنقلة التي تضم عدد كبير من المعالجات. ومن الجدير بالذكر أن عملية الجدولة على أنظمة تضم عدد من التي تضم عدد كبير من المعالجات. ومن الجدير بالذكر أن عملية الجدولة على أنظمة تضم عدد من أمعالجات الغير متجانسة ما زالت غير مكتملة وقيد البحث (NP-complete problem). وهذا يعني أن أفضل قيمة للطاقة المستنفذة و وقت التنفيذ لم يتم تمثيله بخوارزمية على شكل معادلات رياضية. و يجدر الذكر هنا إلى أن الأنظمة التي تضم عدد من المعالجات الغير متجانسة تحتاج إلى نظريات وخوارزميات جدولة معقدة تمكننا من الحصول على أداء جيد لهذه الأنظمة عند إسناد أي عمل عليها.

وفي هذه الأطروحة تم تقديم منهجية يعتمد عليها لاكتشاف تركيبة جيدة من المعالجات الغير متجانسة في أنظمة معالجة تضم عدد كبير جدا من المعالجات الغير متجانسة بهدف الحصول على مقايضة مناسبة بين الطاقة والأداء. المنهجية المقدمة تطبق خوارزمية الجينات لاستكشاف تركيبة جيدة من المعالجات في مجال بحث كبير ومعقد لتنفيذ أي مهمة تسند لهذا النظام.

النتائج التي تم التوصل إليها من خلال التطبيقات والتجارب تظهر الأهداف المراد تحقيقها، بالإضافة إلى عمل تقدير جيد للوقت الذي يحتاجه النظام لتنفيذ مهمة كبيرة على نطاق واسع جدا من المعالجات قبل البدء بعملة التنفيذ الفعلي. وفقا لذلك تم التوصل الر تركيبة مناسبة من المعالجات يتم من خلالها الحصول على أداء جيد للنظام وفق قيود مطبقة على الطاقة المستهلكة باستخدام خوارزمية الجينات.

#### DECLARATION

I declare that the master thesis entitled "Performance-Power Enhancement on High-Scale Heterogeneous Multi Processors (HMP) using Genetic Algorithms (GA)" is my own original work, and hereby certify that unless stated, all work contained within this thesis is my own independent research and has not been submitted for the award of any other degree at any institution, except where due acknowledgment is made in the text.

Ahmad N. M. Aljabari

#### STATMENT

In presenting this thesis in partial fulfillment of the requirements for the master degree in Informatics at Palestine Polytechnic University (PPU), I agree that the library shall make it available to borrowers under rules of the library. Brief quotations from this thesis are allowable without special permission, provided that accurate acknowledgment of the source is made. Permission for extensive quotation from, reproduction, or publication of this thesis may be granted by my main supervisor, or in his absence, by the dean of graduate studies and scientific research when, in the opinion of either, the proposed use of the material is for scholarly purposes. Any copying or use of the material in this thesis for financial gain shall not be allowed without my written permission.

Ahmad N. M. Aljabari

#### ABBREVIATIONS

**ARM** Acorn RISC Machine

CPU Central Processing Unit

**EP** Execution Power

ET Execution Time

GA Genetic Algorithm

HARD History-Aware, Resource-Based Dynamic Scheduling

HMP Heterogeneous Multi Processor

IC Instructions Count

**IPC** Instruction Per Clock

**IP** Information Policy

**ISF** Instruction Set Format

LP location policy

MCP Multi Core Processor

minGW Minimalist GNU for Windows", is a minimalist development envi-

ronment for native Microsoft Windows applications

MIPS Millions of Instructions Per Second

MSYS collection of GNU utilities

**MUTP** Mutation Probability

**NEC** Nippon Electric Company

NP Number of Processor

**OVPsim** Open Virtual Platform Simulator

POPSIZE Population Size (Number of Individual Population)

PSD Processor Sharing Density

PVP Primary Virtual Processor

RP Real Processor

RRDA Round Robin Dynamic Assignment

SP Selection Policy

SD Sharing Data

TLP Thread Level Parallelism

TP Transfer Policy

VP Virtual Processor

VLSI Very Large-Scale Integration

XOVERP Crossover Probability

#### Dedication

I dedicate this study to my parents, my wife, my children, my brothers, my sisters, and my friends for their encouragement, support, endurance, and patience.

#### Acknowledgment

I bow my head to ALMIGHTY ALLAH for the help, guidance and blessing HE has bestowed me.

I am indebted to all who encouraged me to produce this research study. So many people helped during the process of writing the study. I am especially grateful for the encouragement given to me by my supervisor, Dr. Mohammad Aldasht, at various stages of the production of the research study.

To all of you, once again, thank you very much.

Ahmad N M Aljabari

# **Table of Contents**

| 1 | Int | troduction                                                        | 1      |

|---|-----|-------------------------------------------------------------------|--------|

|   | 1.1 | Overview                                                          | 1      |

|   | 1.2 | Problem Statement                                                 | 4      |

|   | 1.3 | Motivations                                                       | 6      |

|   | 1.4 | Objectives                                                        | 7      |

|   | 1.5 | Contribution                                                      | 7      |

|   |     |                                                                   | '      |

| 2 | Ba  | ckground and Literature Review                                    | 9      |

|   | 2.1 | Heterogeneous multi-processor architecture                        | 11     |

|   | 2.2 |                                                                   | 16     |

|   |     |                                                                   | 16     |

|   |     |                                                                   | 16     |

|   | 2.3 |                                                                   | 18     |

|   |     |                                                                   | 19     |

|   |     | AAA IDAD . D                                                      | 20     |

|   |     | 2.3.3 History-Aware, Resource-Based Dynamic Scheduling on HMP ar- | -0     |

|   |     |                                                                   | 21     |

|   |     |                                                                   | 22     |

|   | 2.4 | ~                                                                 | ${23}$ |

|   |     |                                                                   |        |

| 3 | Me  |                                                                   | 24     |

|   | 3.1 |                                                                   | 25     |

|   |     |                                                                   | 25     |

|   |     | 3.1.2 Application/ Behavior Problems:                             | 26     |

|   |     | 3.1.3 Processor Specifications                                    | 26     |

|   | 3.2 | Scheduling Algorithm Pseudo Code:                                 | 27     |

|   | 3.3 | Scheduling Algorithm Details                                      | 28     |

|   | 3.4 | Genetic Algorithm                                                 | 36     |

|   |     | 3.4.1 GA Details                                                  | 36     |

|   |     | 3.4.2 Scheduling Algorithm Constraints                            | 42     |

| 4 | D   |                                                                   |        |

| 4 | -   |                                                                   | 15     |

|   | 4.1 |                                                                   | 45     |

|   | 4.2 |                                                                   | 46     |

|   |     |                                                                   | 46     |

|   |     |                                                                   | 48     |

|   |     | 4.2.3 Matlab R2007b                                               | 48     |

|    | 4.3<br>4.4 | Challenges and Difficulties during Implementations       4         Experiments and Results       4         .4.1       Phase 1. Accuracy of Estimation Execution Time       4         .4.2       Phase 2: Overhead       6         .4.3       Phase 3: Power - Performance Tradeoff       7 | 9<br>9 |

|----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 5  | Con        | usion and Future Work 8                                                                                                                                                                                                                                                                    | 1      |

|    | 5.1        |                                                                                                                                                                                                                                                                                            | -      |

|    | 5.2        | Discussion                                                                                                                                                                                                                                                                                 | 4      |

|    | 0.4        | 8                                                                                                                                                                                                                                                                                          | 5      |

|    | 5.3        | uture work                                                                                                                                                                                                                                                                                 | 7      |

| Bi | bliog      |                                                                                                                                                                                                                                                                                            |        |

| Aŗ | openo      | ces 9.                                                                                                                                                                                                                                                                                     | 3      |

# List of Figures

| $1.1 \\ 1.2$                                      |                                                                                                                                                                                                                                                                                                                                                              | 5<br>6                                 |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| $2.1 \\ 2.2 \\ 2.3 \\ 2.4 \\ 2.5$                 | Different Processors Design on Same Silicon Die Area                                                                                                                                                                                                                                                                                                         | 12<br>15<br>15<br>20<br>21             |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7     | Scheduling Algorithm Part       Proposed Algorithm Flowchart         Proposed Algorithm Flowchart       Mapping Virtual Platform to Real         Mapping Virtual Platform to Real       Effect of Population Size on Search Accuracy in GA         Effect of Crossover Size on Search Accuracy in GA       Effect of Crossover Size on Search Accuracy in GA | 28<br>29<br>31<br>34<br>38<br>41<br>42 |

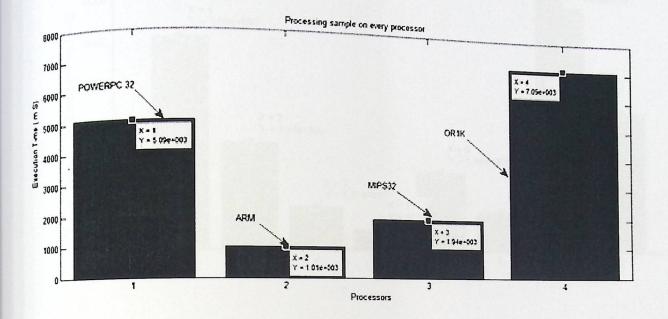

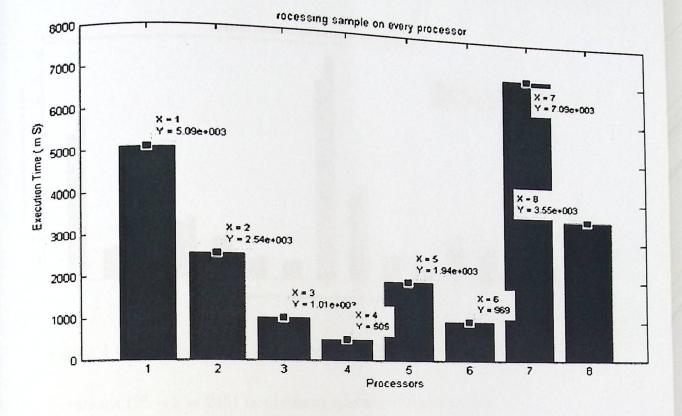

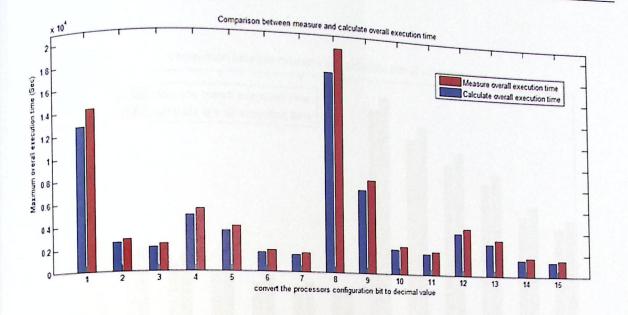

| 4.1<br>4.2<br>4.3<br>4.4                          | Execution Time for One Sample among 4 ProcessorsExecution Time for One Sample among 8 ProcessorsEstimated and Measured Execution Time for 4 Processors                                                                                                                                                                                                       | 51<br>58<br>59<br>60                   |

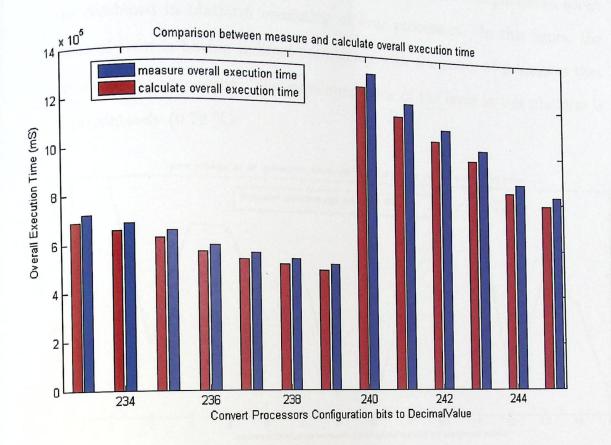

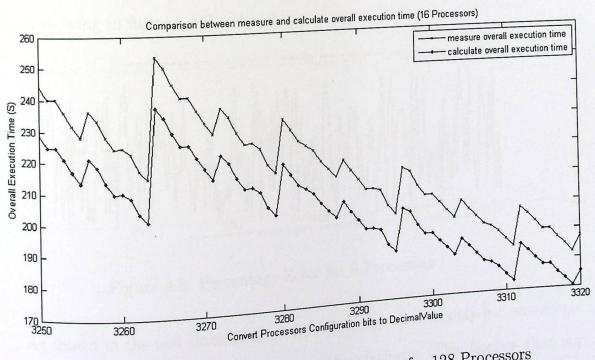

| <ol> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ol> | Estimated and Measured Execution Time for 128 Processors                                                                                                                                                                                                                                                                                                     | 61<br>61<br>62                         |

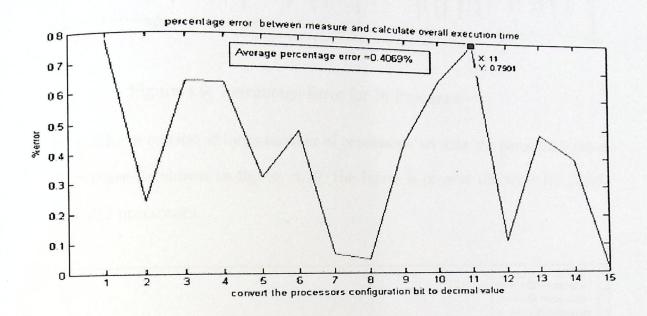

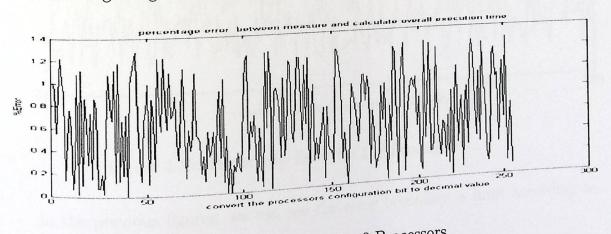

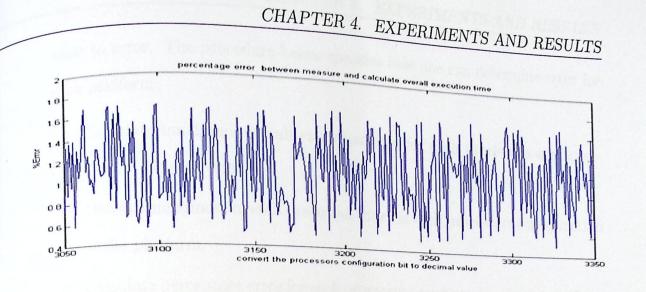

| 4.8<br>4.9<br>4.10                                | Percentage Error for 8 Processors                                                                                                                                                                                                                                                                                                                            | 62<br>63                               |

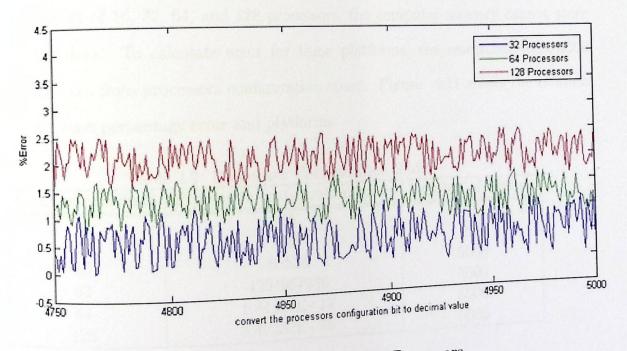

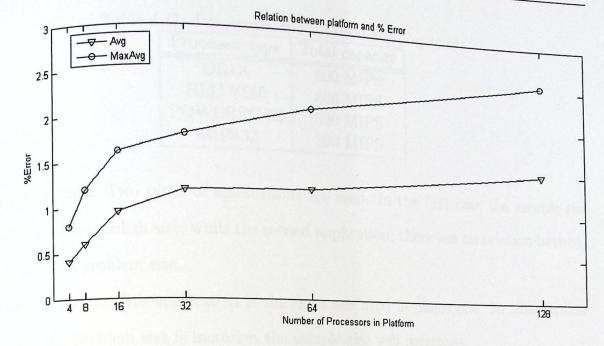

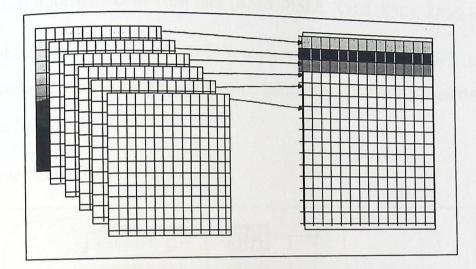

| $4.11 \\ 4.12$                                    | Percentage Error Relative to Number of Processors                                                                                                                                                                                                                                                                                                            | 63<br>65<br>67                         |

| 4.14                                              | Processing Environment                                                                                                                                                                                                                                                                                                                                       | 67<br>68<br>69                         |

| $4.16 \\ 4.17$                                    | Sample Execution Time for Images Application                                                                                                                                                                                                                                                                                                                 | 69<br>70<br>70                         |

| 4.19                                              | Overhead Ratio for LU Application                                                                                                                                                                                                                                                                                                                            | 71<br>71                               |

#### LIST OF FIGURES

| 4.21 | 1 GA Environment System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |   |   |   |   | 79 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|----|

| 4.22 | 2 Benchmarks Execution Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • | • | • | • | • | 13 |

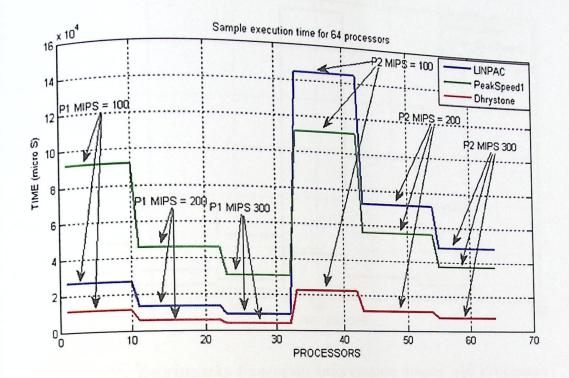

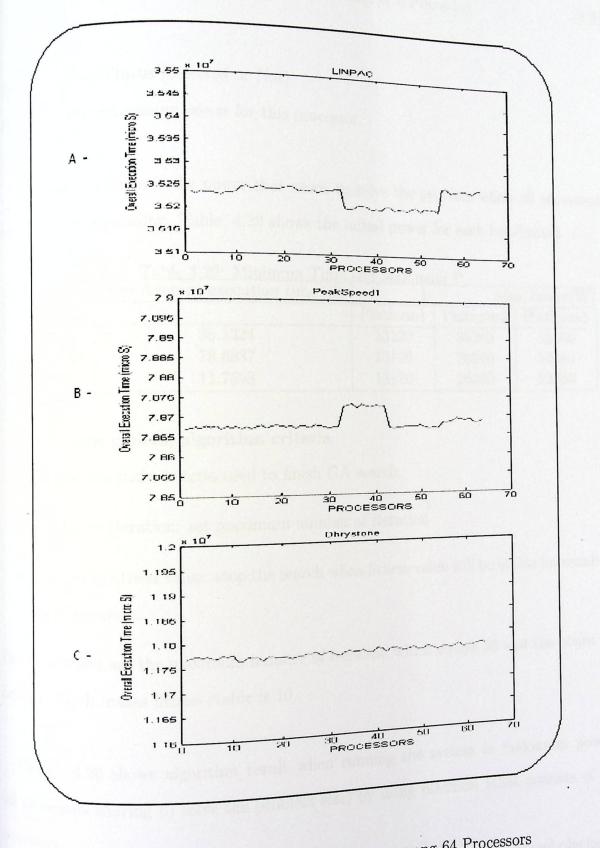

| 4.23 | 2 Benchmarks Execution Information among 64 Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • | • | • | • | • | 77 |

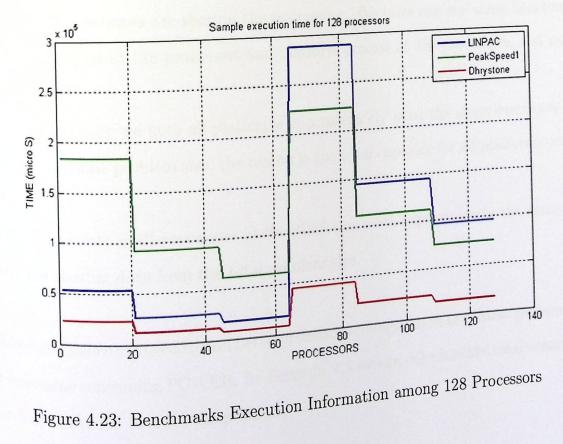

|      | Denominarias Execution Information among 128 Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |   |   |   |   | 77 |

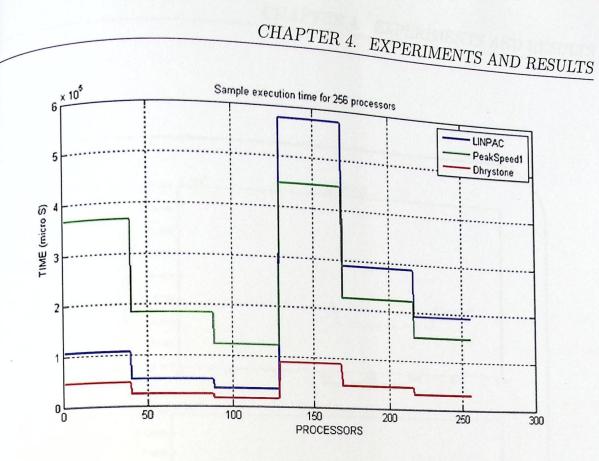

|      | Denominarias Execution Information among 256 Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |   |   |   |   | 70 |

| 1.20 | Denominarks Execution Time among 64 Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |   |   |   |   | 70 |

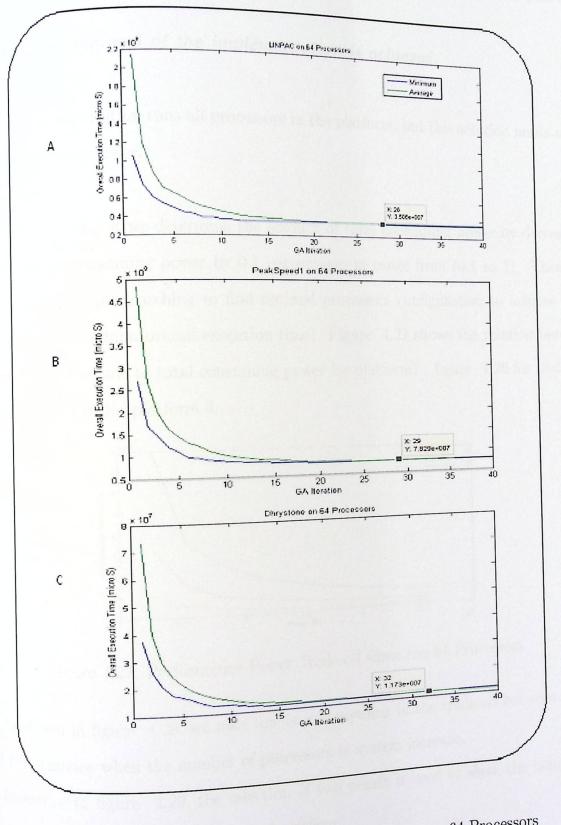

| 4.26 | 6 Max. Performance when Executed among 64 Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • |   | • | • |   | 01 |

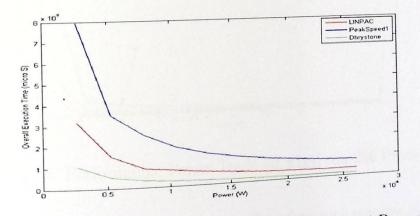

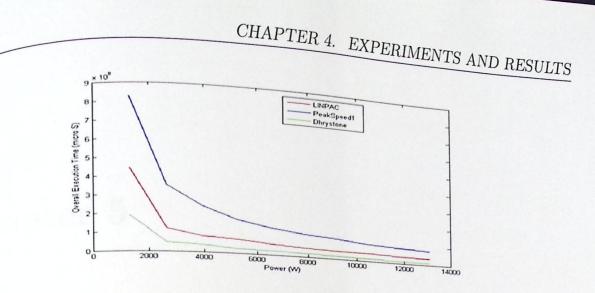

| 4.27 | 7 Performance Power Trade off when run 64 Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • | • | • | • | • | 01 |

| 4 28 | 8 Performance Power That of the last of th | • |   |   | • |   | 82 |

| 1.20 | 8 Performance Power Trade off when run 128 Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |   |   |   |   | 83 |

| 4.29 | Performance Power Trade off when run 256 Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |   |   |   |   | 83 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   |   |   |   |    |

| 5.1  | Percentage Error Relative to Processors Count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |   |   |   |   | 85 |

# List of Tables

| $1.1 \\ 1.2$                    | Threads Behavior Characteristics                                                                                                                                                                          | 5<br>6 |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| $2.1 \\ 2.2$                    | high Scale HMP Model                                                                                                                                                                                      | 12     |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Virtual Platform Mapped to Real Platform         Processors Specification Assumption         Execution Time and Power Information         Processors PSD         PS and Executing Time for Each Processor | 31     |

| 4.1                             | Processors Specifications                                                                                                                                                                                 | 50     |

| 4.2                             | LU Application Files                                                                                                                                                                                      | 55     |

| 4.3                             | Platform Consists of 4 Processors                                                                                                                                                                         | 57     |

| 4.4                             | Platform Consists of 8 Processors                                                                                                                                                                         | 57     |

| 4.5                             | Platform Consists of 16 Processors                                                                                                                                                                        | 57     |

| 4.6                             | Platform Consists of 32 Processors                                                                                                                                                                        | 57     |

| 4.7                             | Platform Consists of 64 Processors                                                                                                                                                                        | 57     |

| 4.8                             | Platform Consists of 128 Processors                                                                                                                                                                       | 57     |

| 4.9                             | Processors Configuration Slides                                                                                                                                                                           | 64     |

| 4.10                            | Different Platforms Processor Count                                                                                                                                                                       | 65     |

| 4.11                            | Processors Specification and Capacity                                                                                                                                                                     | 66     |

| 4.12                            | Processors Specification                                                                                                                                                                                  | 67     |

| 4.13                            | benchmarks behavior                                                                                                                                                                                       | 73     |

| 4.14                            | Platforms Combination                                                                                                                                                                                     | 74     |

|                                 | Real Processors Specification                                                                                                                                                                             | 74     |

|                                 | Experiment Program Files                                                                                                                                                                                  | 75     |

|                                 | Platform Combination, Consist of 64 Processors                                                                                                                                                            | 75     |

|                                 | Platform Combination, Consist of 128 Processors                                                                                                                                                           | 76     |

|                                 | Platform Combination, Consist of 256 Processors                                                                                                                                                           | 76     |

|                                 | Minimum Time and Maximum P                                                                                                                                                                                | 80     |

|                                 |                                                                                                                                                                                                           |        |

.

# Chapter 1

# Introduction

This chapter introduces a general overview of the present research, its problem statement, objectives, motivations and finally its major contributions to the field. This chapter is organized as follows: section 1.1 is an overview about the study or the thesis; section 1.2 describes the problem statement; section 1.3 introduces the objectives of the thesis; section 1.4 lists the motivations of the study; and section 1.5 includes the thesis contributions.

#### 1.1 Overview

The computer system consists of variety components (CPU, Memory, I/O device, etc.) Each component in the system is responsible for a particular job during the execution such as, memory to load code, I/O device to input/output data, system bus to connect between components, etc. The primary component in the system is the central processing unit (CPU). The original CPU consists of a single processing core that executes the program code in a sequential mode (instruction by instruction). Computing performance is improved by increasing the execution speed to the CPU, for example; by increasing the clock frequency for the processor unit. In the recent years, this approach was abandoned due to some challenges (increased core complexity, energy and heat cost, limiting the rate at which the clock speed can be increased, etc.) [18]. Parallel programming is another technique which has been developed to increase the performance of a single processor. Parallel programming is applied by using different methods like pipelining, VLSI, and superscalar. However, parallel programming methods have limitations. For example, the pipeline method throughput is generally less than the number of pipeline stages. In addition, there are limitations in parallel level in the program itself, and the parallel programming technique is still weak to meet the needs for high performance in the computing system [10, 43].

For these challenges, new trends were adopted for multiprocessor architecture approach by either adding more core in the chip or adding more processor units to increase computer system performance. Each processor unit is responsible for executing its own sequence of instruction to increase the overall computing system performance. The multiprocessor architecture is a good method to improve such performance. Amdahl's Law reveals the maximum speed up that can be expected from parallel algorithms given the proportion of parts that must be computed sequentially [21].

There are two types of multiprocessor architecture: homogeneous and heterogeneous. The first one is also called symmetric. In this type, the platform consists of identical processors. The second type, heterogeneous multiprocessors (HMP) architecture, is called asymmetric; HMP architecture consists of variety processors on one chip. There are two different types of HMP architecture: performance heterogeneity, which uses the same instruction set architecture "ISA" and functional heterogeneity where each core has an instruction set architecture.

Homogeneous type provides a uniform platform on which parts of the computer programs are executed equally on all processors. However, the homogeneous platform may not provide the best possible level of performance. To execute different applications of the different parts from the same application, we need different processing requirements. The benefits of multiprocessors can be achieved by executing different program parts on different processors capability or more specialized processors. The implementation on HMP system might be more complicated. This needs more information of program behavior and processor types when matching between the processors and the threads to achieve high performance.

While the HMP has the potential to increase performance, the designed any program on HMP could be difficult. The programmer not only deals with concerns implicit in concurrent programming on HMP such as scalability, synchronization, consistency, and deadlock prevention, but also with different processor types, instruction set architecture, and thread behavior characteristics so as to schedule threads on processors and achieve high performance [30].

In multiprocessors architectures, parallel programming has different methods when compared to a single processor. Multiprocessors technique can exploit thread level parallelism (TLP) methods. The program or application will decompose to different parts depending on decomposing methods. There are two methods applicable to decompose the application into a small part: functional (task) decomposition and data (domain) decomposition. Each part (thread) will be executed on a processor. With Parallel programming and TLP, we can exploit multiprocessors system architecture, especially HMP architecture when executing threads with different processing requirements [43].

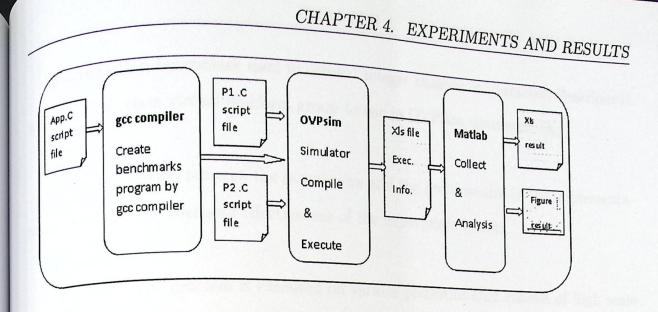

The present study aims to exploit high scale HMP architecture by applying genetic algorithm scheduler on different processor types without any intervention from programmers, to achieve optimized performance with minimal concumption power, and to make the assignment of threads to the processors responsible for the runtime system. Scheduling algorithm on high scale HMP architecture will be implemented by using OVPsim simulators and Matlab [3,42]. The OVPsim simulator supports many types of processors such as mips32, arm, PowerPC 32, and NEC v850. These processor types are used to build the computer processing environments. The benchmarks selected in the implementation support multiprocessor platform environment.

### 1.2 Problem Statement

In general, laptops, desktop computers, and servers use homogeneous multiprocessor architecture to move away from complexity. Some applications focus on using HMP architecture, particularly the applications that have a special purpose such as image/video processing applications.

Addressing the difficult methods used to decide which thread will be assigned to processors during the runtime to achieve high performance occurs by exploiting the HMP system. The scheduler relies on the program characteristic behavior in the runtime environment and the processor's processing capability to make the system decide which thread-processor matching is better to achieve high performance with minimal power.

To achieve this, the study is developed through the following stages:

- Step1. Selecting a simulation environment and a set of benchmark applications to achieve the experimental work of the research.

- Step2. Developing cost function algorithm that will be able to collect program behavior characteristic information for each processor, processing requirements, execution behavior and inter-thread communication.

- Step3. Developing an evolutionary scheduling algorithm that uses the program behavior characteristics and processor characteristics to optimized performance and decrease power consuming.

- Step4. Analyzing the results and achieving comparison to decide the quality of the

proposed algorithm and realize the required enhancements which lead to a better algorithm.

#### Problem example:

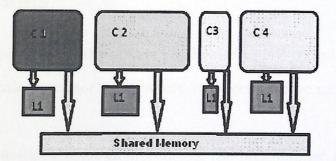

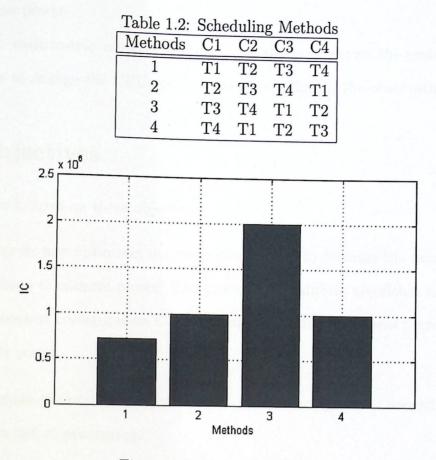

By using different methods to schedule thread-processor, we can achieve different performance. We use an architecture system that consists of 4 heterogeneous processors (C1, C2, C3, and C4) as shown in figure 1.1. The application that needs to be executed consists of 4 threads (T1, T2, T3, and T4). Each thread consists of 1 million instructions and has an instruction per clock (IPC) behavior characteristic for each processor as shown in Table 1.1.

Table 1.1: Threads Behavior Characteristics

| Thread | C1  | C2  | C3  | C4  |   |

|--------|-----|-----|-----|-----|---|

| T1     | 1.4 | 2.4 | 0.5 | 1.2 | Í |

| T2     | 0.5 | 1.5 | 1   | 0.5 |   |

| T3     | 2   | 0.5 | 2.4 | 3.2 |   |

| T4     | 2.6 | 1   | 1.6 | 1.4 |   |

| 14     | 2.6 | 1   | 1.6 | 1.4 |   |

Figure 1.1: Processors Interconnection

By using 4 processors to execute 4 threads, we have 16 different combinations to execute the program. In the example, we will show 4 different combinations. The results are shown in figure 1.2 by executing the programs using 4 scheduling methods as explained in table 1.2.

Figure 1.2: Execution Results

### 1.3 Motivations

Scheduling on heterogeneous multiprocessors is defined as NP-complete problem [23,31] . The work on high scale processor architecture is expected to be more complicated.

In heterogeneous multiprocessor environments, the programmer must deal with high scale HMP architecture characteristic to write a program that uses the heterogeneity of the system to achieve high performance. In this work, the scheduling algorithm will assist the programmer to write a program without dealing with HMP architecture to build a program that can observe the system during the run time to perform thread-processor scheduling in high scale HMP architecture to achieve high performance. In addition to developing the computing system by integrating a new option that controls the processing performance according to power status; this option will work through two methods:

First: manual control method: the user increases or decreases the overall perfor-

mance to save power.

Second: automatic control method: the system observes the power source status or peak time to change the CPUs performance according to the observation information.

### 1.4 Objectives

This research focuses on three objectives:

- To integrate new options in the computing system to decrease the value of consuming power from maximum power. The proposed scheduling algorithm is responsible to find processor configuration that guarantees to achieve optimal performance within minimal power.

- To estimate the overall execution time and consuming power needed to execute the problem before processing.

- To distribute the any problem to all processors according to processor's capability.

### 1.5 Contribution

Estimating the power consumption and time needed to execute programs on high scale HMP architecture before executing takes place by:

- Presenting the program by small sample (S) that specify the real phenomena of the program.

- Determining the program problem size.

- Executing sample (S) on each processor and measuring the time and power needed for each processor.

- Estimating the consumption power and execution time when using all processors.

- Setting the processor configuration of the high scale HMP architecture by using GA.

• Estimating the overall power and time needed to execute the program according to the processor configuration, sample power and time for each processor, and program size.

This thesis presents information about how to assist the system to exploit high scale HMP architecture by carrying out dynamic thread scheduling that increases the performance with minimal power in a number of ways:

- Abstracting the program behavior characteristic during the run time execution.

- Developing a cost function that uses a program's behavior characteristic to inform thread placement across heterogeneous processor.

- Developing an evolutionary scheduling algorithm that exploits both the program behavior characteristics and processor characteristics to optopmize performance and minimize power consuming.

# Chapter 2

# **Background and Literature Review**

The purpose of this chapter is to provide a theoretical background about the scheduling algorithms which are implemented on multi / many processor architectures. In addition, this chapter reviews the literature about the development of scheduling algorithms for heterogeneous multi-processor architectures. The chapter is divided into sections as follows: Section 2.1 presents an overview about two general types of scheduling in HMP architecture. Section 2.2 presents the general scheduling methods. Section 2.3 presents the recent method proposed to schedule HMP architecture.

In general, processor performance enhancement focuses on increasing clock frequency rate and parallel processing by applying instruction level parallelism technique in single processor (improving single thread performance). However, these techniques are stalled due to the limitations in the degree of parallel processing that can be extracted from sequential processing [46] and the clock frequency issues (energy, heat, and complexity) [39]. The idea is to increase computing system performance by designing a platform which consists of multi processors with multicores [35]. The multi-core processor is designed by exploiting available transistors on a given size of processor die. With this generation of multi-core processors, we can exploit thread level parallelism [21]. Multi-processors platform can be symmetrical (homogeneous); in this type all processors in the chip are identical. Most computing systems are homogeneous. Asymmetrical (heterogeneous) HMP architectures consist of different types of processors; each processor has different function (ISA), performance, and capabilities [8].

HMP architecture has better performance than the homogeneous type [9]; the disadvantage of using HMP architecture is limited to the complexity of exploiting the heterogeneity in the implementations. There are different methods used to schedule threads on processors. These methods can be classified into static and dynamic scheduling algorithms [12].

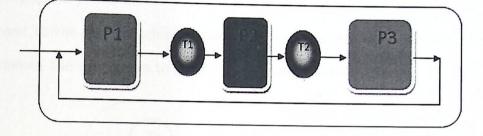

In order to exploit Thread Level Parallelism (TLP), the application can be decomposed by two methods: function decomposition and data decomposition. In order to use function decomposition, the task splits into small tasks. Each task is run by a special processor depending on the efficiency and the executing thread on any processing type (in HMP architecture) or on any processor (in symmetric architecture). In order to using data decomposition, when the executing application has large data, we split the database boundary into small parts and distribute these parts to the processors; each processor will execute the same function [27, 32, 38, 43].

When the executing application uses any type of decomposition, dependency must be controlled to save the consistency and accuracy. There are many methods used to save implicit execution property like share memory, massage passing, and mailbox. The present study proposes some methods and techniques that can be used to schedule threads in HMP architecture in order to increase throughput and system performance.

# 2.1 Heterogeneous multi-processor architecture

Computer systems that use multi-processors (heterogeneous resources) are not new. The IBM System/709 incorporates a processor to process I/O operation. In this case, the main CPU executes another operation during I/O operation [19]. The same technique can be found in another system such as IBM System/370, System/360 [13], and Control Data CDC 6600 [42]. These processors are generally limited to performing special purpose operation (transfer and signaling operations) and not sharing the computer system capabilities. There is another specific purpose processor which has been used to string matching [15], accelerate floating points [14], encryption [47] and many other applications. [30] proposes that HMP architecture consists of general purpose processors (CPU), unlike the superscalar processors that have specific purpose processors.

HMP architecture has been recently used in specialist applications such as image/video applications, network processing, and low power embedded systems. some primary implementations of HMP architecture:

- Network processing equipment uses a number of processors like, the IBM Power NP [7], Intel IXP [5], and Motorola C-Port [20].

- Multimedia workloads and scientific computation use IBM Cell processors [1,22].

- Low power embedded devices, such as mobile phones, use Intel PXA800F [29].

In this research, we are not talking exclusively about HMP archetecture. However, the research extends a wide range of high scale HMP archetecture. Some models of high scale HMP archetecture are shown in table 2.1 [1].

When the transistors count are increased, the expected performance will be improved. In general, performance increase is governed by Pollack's Rule [11]. This means that the expected performance will be increasing by square root of increasing the transistor count. For example, doubling the number of transistors in a single processors will increase the

| Table 2.1: high Scale HMP Model                                                                                             |                           |                               |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------|--|--|--|--|--|

| Processor                                                                                                                   | NP                        | Manufacturer                  |  |  |  |  |  |

| TSUBAME 2.0 - HP ProLiant SL390s G7 Xeon 6C X5670<br>K computer, SPARC64 VIIIfx 2.0GHz<br>Cielo - Cray XE6, Opteron 6136 8C | 73278<br>705024<br>142272 | NEC/HP<br>Fujitsu<br>Cray Inc |  |  |  |  |  |

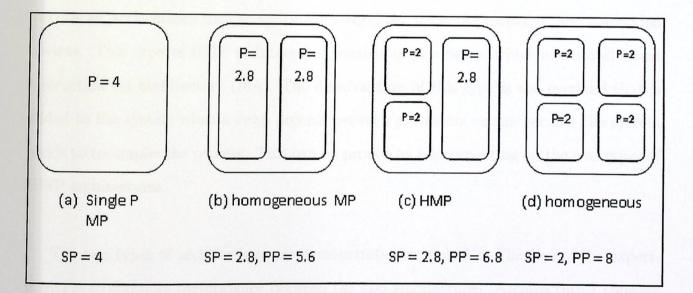

performance about 40%; on other hand, doubling the number of processors will increase the performance about 100% in case of parallel workload. Figure 2.1 explains how we can achieve different performance from the same area of silicon when the processor design is improved. Figure 2.1(a) presents a single processor, whereby the overall execution performance for a sequential program equals 4. As shown in Figure 2.1(d), if we can exploit all processors at the same time with the executing parallel program, we can achieve performance which is equal to 8. With high degree of complexity to design more processors from the same area of silicon die, we can increase the performance as shown in 2.1(b, c, and d).

Figure 2.1: Different Processors Design on Same Silicon Die Area

As we noted earlier, processor architectures can be divided into two types: homogeneous and heterogeneous multi-processor architectures. Homogeneous multi-processor architectures, also called symmetric, consist of identical processors. In general, implementation depends on homogeneous type, specially the computers, which have general purpose programs, like laptops, servers, and desktops [36]. Heterogeneous multi-processor architectures, also called asymmetric HMP architecture, consist of a variety of processors. The following is an explanation of the two main domains of heterogeneity:

**Processors with different performance**: these are processors with high performance and are used to process big threads and processors with low performance and used to process small threads to reduce consuming power and exploit thread level parallelism. In this type of variety, all processors on the platform use the same instruction set architecture (ISA), and there is no need to recompile threads in case of swapping between the processors.

**Processors with different ISA (function)**: these processors can be found in the applications that have specific purpose. The developer enhances the system by adding processors that can execute some function with high degree of performance to improve the overall performance such as multimedia workload, network processing, and embedded devices. This type of HMP architectures consists of processors, which execute different instruction set architecture (ISA). The disadvantage of this type is the overload that is added to the system when a swap process between processors occurs because the system needs to recompile the process. This can be proved by experimenting on the two types of HMP architectures.

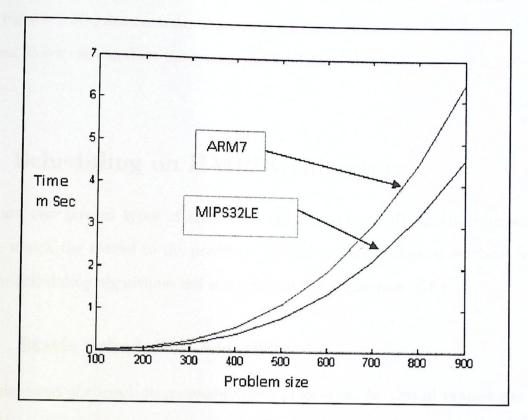

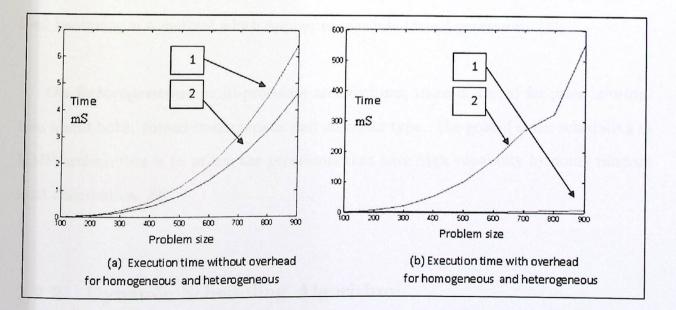

The two types of architectures are demonstrated in table 2.2. The goal of the experiments is to compare performance between the two architectures. Architecture 1 consists of two processors which differ in performance (processor 0 =MIPS32LE has capability of 300 MIPS; processor 1=MIPS32LE has capability of 100 MIPS). Architecture 2 consists of two processors which differ in function (processor 0 =MIPS32LE has capability of 300 MIPS; processor 1=ARM7 has capability of 100 MIPS). The source code used to create architecture 1/2 are shown in Appendix A.1 and A.2.

| Architecture             | e 1 (performat | nce HMP) | Architecture 2 (functional HMP) |          |      |  |

|--------------------------|----------------|----------|---------------------------------|----------|------|--|

| Processor                | -3PC           | MIPS     | Processor                       | Туре     | MIPS |  |

| Processor0<br>Processor1 | MIPS32LE       | 100      | Processor0                      | MIPS32LE | 300  |  |

| 1 TOCESSOI 1             | MIPS32LE       | 300      | Processor1                      | ARM7     | 100  |  |

Table 2.2: Processors Specification

This experiment will implemented by using OVPsim simulator environment. Two processors will execute the same program shown in Appendix B.1. The program consists of two threads, each of which is used to multiply two matrices. The program will execute 9 times. In each iteration, the size of matrix will increase, and the size of the matrix in each thread will be equal.

Figure 2.2 and Figure 2.3 shown the results for architecture1 and architecture 2 respectively. In each iteration, we can observe the number of instructions executed by each processor and the time needed to execute these instructions for each processor without overhead. We can also measure the overhead needed for each platform, and measure the total time (overhead + execution).

The difference between the two processor architectures in processor1; replacement of processor1 in architecture1 from ARM7 100 to MIPS32LE 100.

Figure 2.2 shows the cooperation execution time (performance) between two processors with the same capability. As can be seen from Figure 2.2, the ARM7 processor is faster than MIPS32LE. The difference in speed for each processor is due to the instruction set architecture format for each processor.

In figure 2.3(a), we can compare the execution time for two architectures without overhead. Architecture1, which consists of processors different in function, is faster than architecture 2, which consists of processors different in performance, because architecture1 contains an ARM7 processors that have capabilities better than MIPS32LE which is used in architecture2.

Figure 2.2: Performance of Separate Processors

Figure 2.3: Execution Time for Homogeneous and Heterogeneous

However, in overall execution time (processor processing time + system overhead time), Figure 2.3(b) demonstrates that architecture 2 is better than architecture1 because overhead factor coming from the system recompiles the thread to the new instruction set format.

# 2.2 Scheduling on HMP Architecture

There are two general types of scheduling algorithms on HMP architecture which are used to match the thread to the processor to achieve high performance; these types are dynamic scheduling algorithms and static scheduling algorithms [25]:

### 2.2.1 Static Scheduling Algorithm:

The assignment of threads to processor before processing. No thread swapping or assignment change between processors during runtime.

On homogeneous multi-processor architectures, there is no need for prior information about thread characteristic and processor type needs to schedule. In general, the load balancing is a method which applies to schedule thread processors [27].

On heterogeneous multi-processor architectures, there is a need for prior information about both: thread characteristic and processor type. The goal of static scheduling in HMP architecture is to utilize the processors that have high capability by doing random load distribution [9].

### 2.2.2 Dynamic Scheduling Algorithm:

Re-assignment of threads to the processor during processing according to thread behavior characteristics.

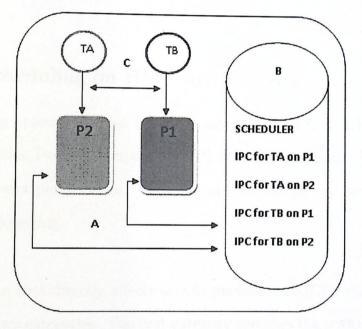

There are many policies which must be considered to decide which method or algorithm is better to dynamic schedule threads in multi-processor architectures. Dr. Aldasht proposes using genetic algorithm to explore the overall policies that define the dynamic load balancing strategies [6].

The first policy, the information policy (IP), is used to determine how the information exchange between nodes. If IP=1, the information will exchange according to load balancing frequency. If IP=0, the information will exchange on demand.

The second policy, the transference policy (TP), is used to specify the case of nodes. If TP = 0, the node is overloaded and needs to transfer the tasks (sender initiator). If TP=1, the node is ready to receive the tasks (receiver initiator). If TP = 2, we have a sender initiator and a receiver initiator at the same time (symmetric initiators).

The Third policy, the location policy (LP), is used to determine which node is incorporated in load balancing operation. If LP=0, that means the information collected from the node is compared with the threshold to decide to which location the node will send or receive tasks. If LP=1, that means the decision will be according to two-thresholds. If LP=2, the node will send tasks to the shortest-path based node, with the lower load. If LP=3, the node will select a random location node as a receiver or sender.

The fourth policy, the selection policy (SP), refers to the task selected to transfer the preemptive (SP=0) or non-preemptive (SP=1) from the sender node. These policies, which are defined by Aldasht, cover all dynamic and static scheduling methods for multicore processers. By tuning the policies during the runtime and checking the overall system performance, THE scheduling algorithm set the value for each policy according to program behavior characteristics.

### 2.3 Literature review

At first glance, when we talk about the distribution of tasks on a multi-processor architecture, we propose using the theory of load balancing on a multi-processor architecture as David W. Holmes does by applying H-Dispatch algorithm to a wide range of numerical simulation problems by using spatial decomposition to create "orthogonal computational tasks." This algorithm makes efficient use of memory resources by limiting the need for garbage collection and taking optimal advantage of multiple processors through employing a "hungry pull strategy" [16]. This algorithm is flexible and efficient when it is applied to a numerical domain, depending significantly on data sharing, regardless of the type of multi-processor: homogeneous or heterogeneous. Nevertheless, if the database domain is used on a heterogeneous multi-processor architecture, it is necessary to develop this algorithm to do data decomposition and distribution depending on the specification and processing type of the processor.

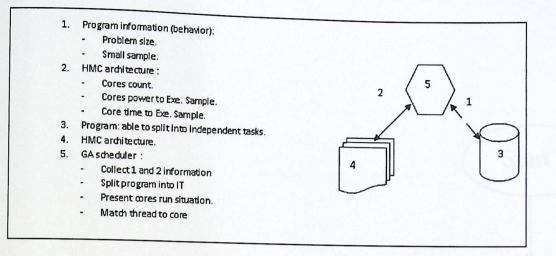

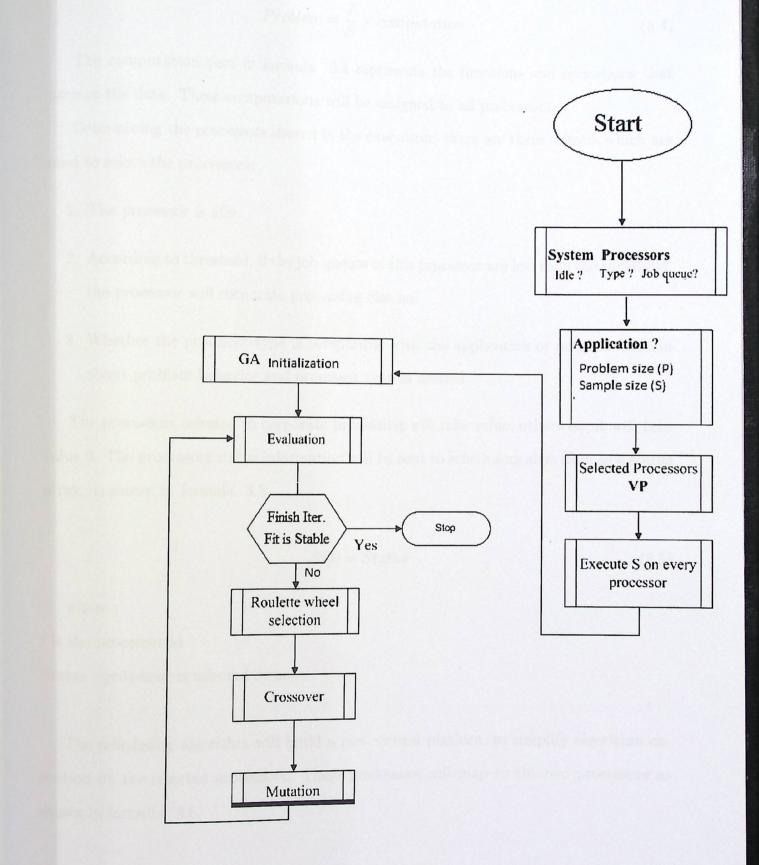

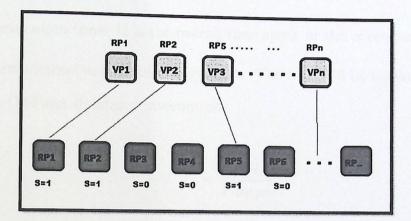

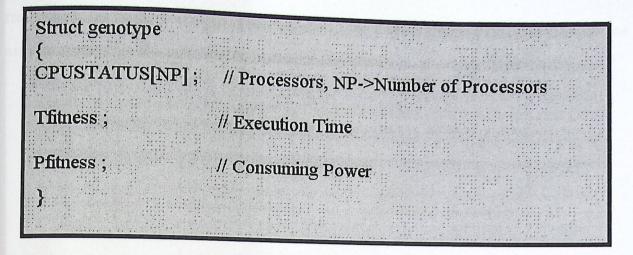

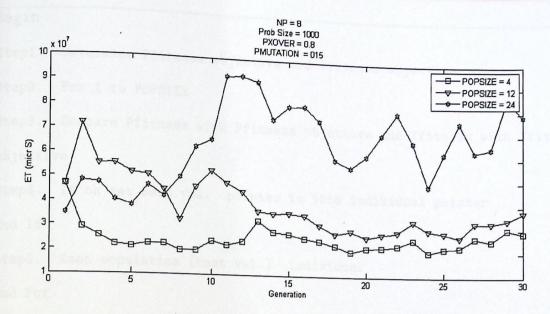

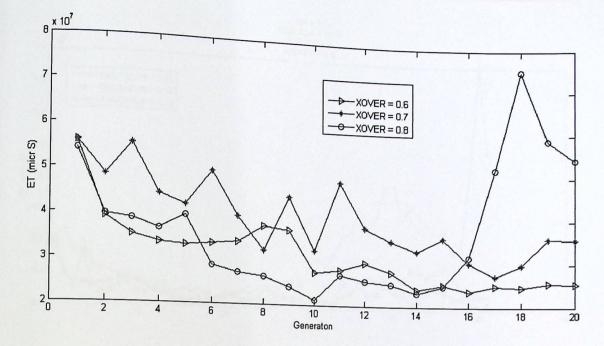

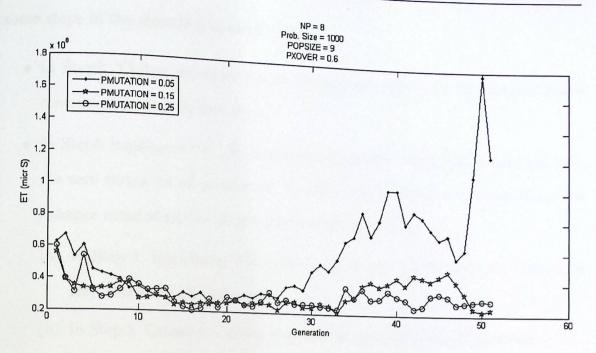

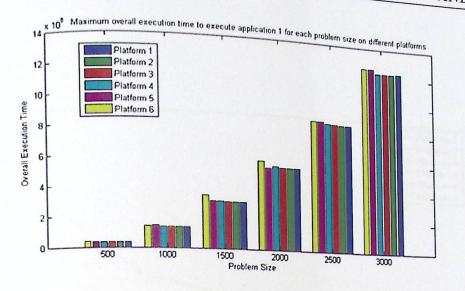

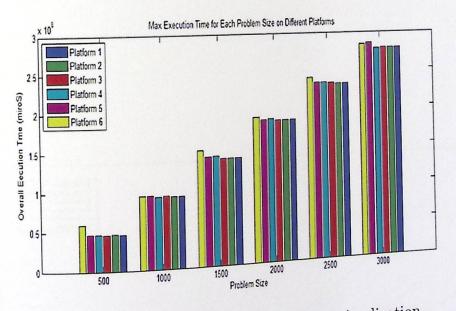

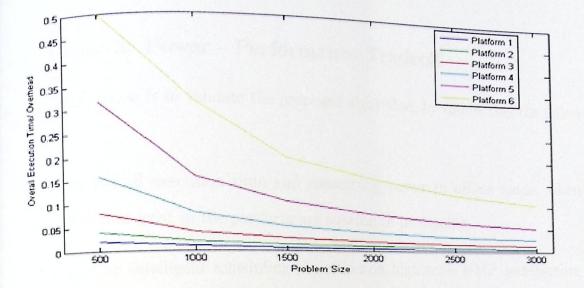

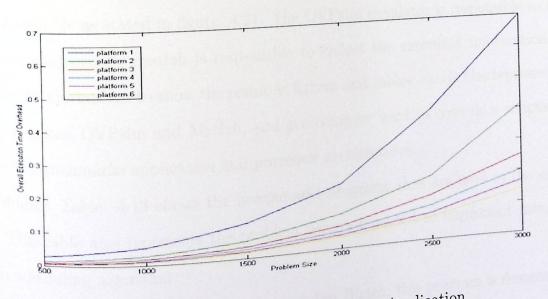

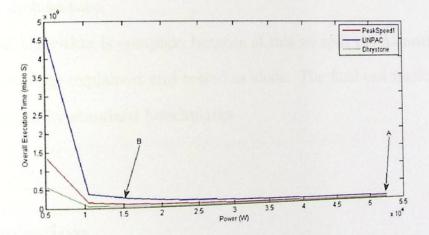

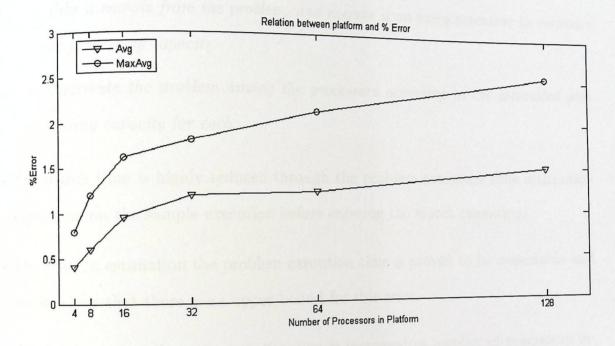

Many recent works have tried to handle the above mentioned problem. Jian [16], tries to exploit the efficiencies of the heterogeneous multi-processor architectures by executing the processes on a smart scheduler which obtains a high performance and consumes power. There are many proposed scheduling algorithms; each depends on some properties from the system to achieve dynamic scheduling such as History-Aware Resource-Based Dynamic Scheduling (HARD). As for the heterogeneous multi-processor architectures proposed by Jooya, this algorithm depends on recording application resources, utilization and throughput, and analyzing the information to decide how to adaptively change the matching between the processes and the processors during the runtime [26]. The above authors wonder how it would be possible to develop the scheduling algorithm by mixing new information to make the algorithm more efficient.